CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

116 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

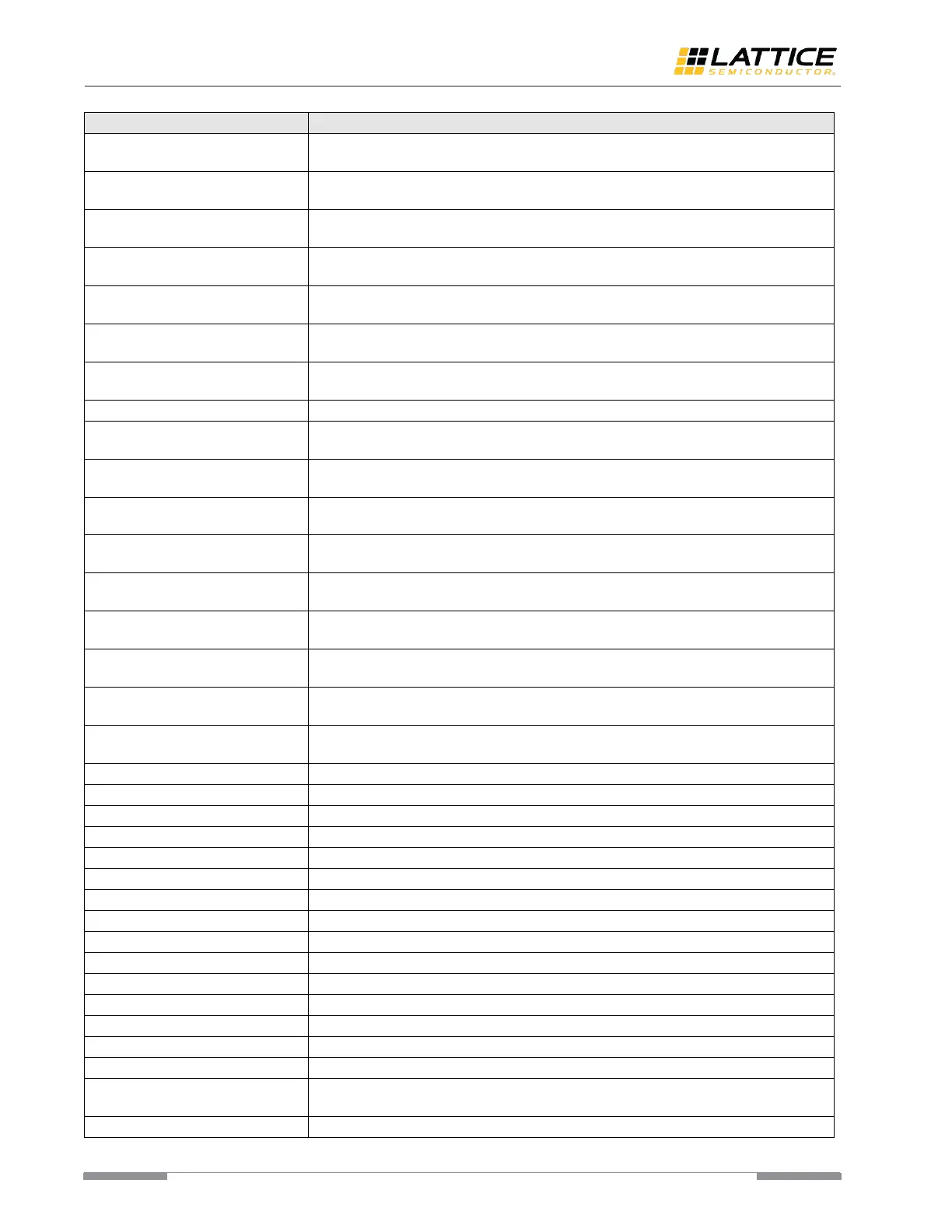

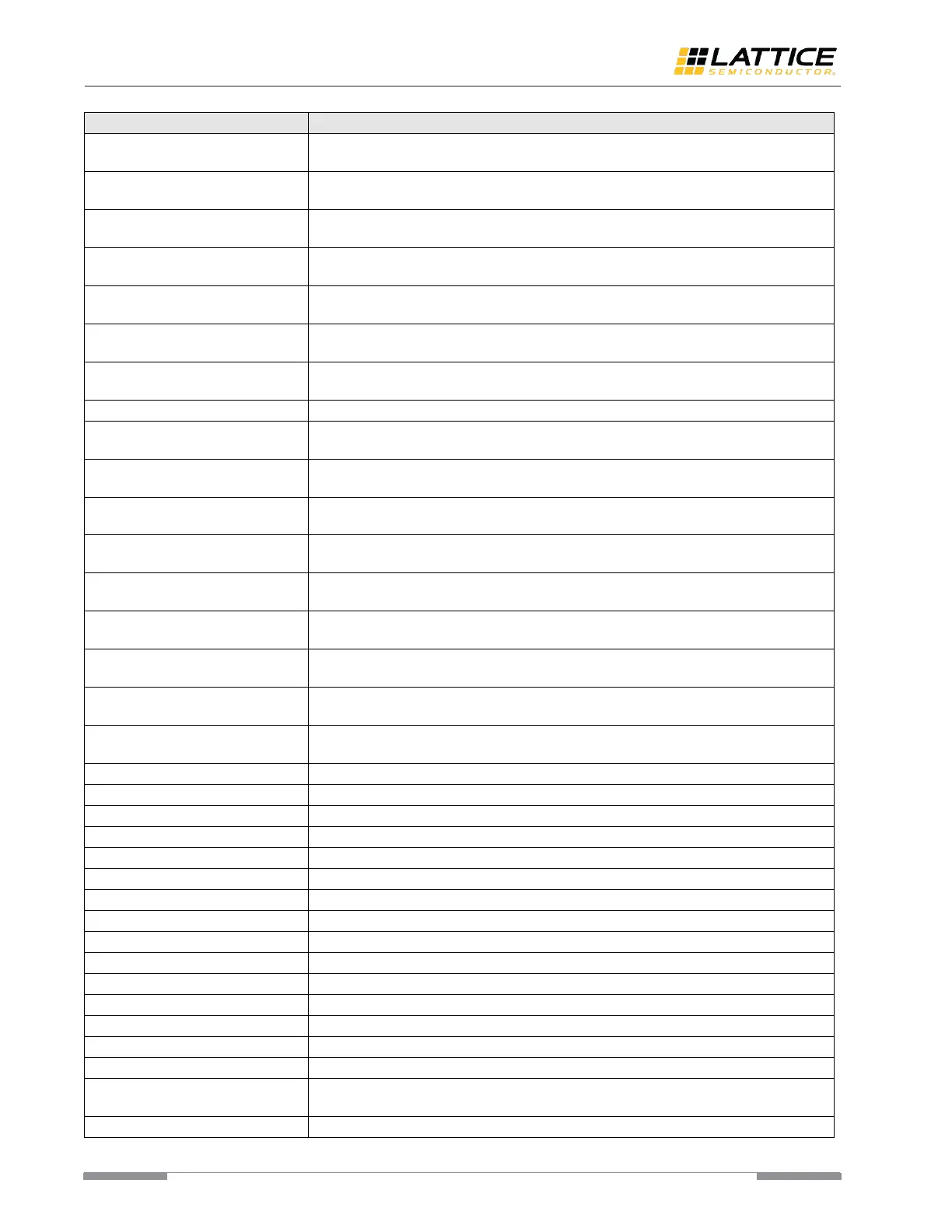

When enabled, MPCS module soft resets the TX path (not including the register space).

For more details, refer to register field tx_mpcs_rst in Table A. 32.

TX Phase Compensation FIFO

Specifies whether the TX phase compensation FIFO is enabled or disabled. For more

details, refer to register field tx_fifo_dis in Table A. 32.

Specifies whether the 8b10b encoding is enabled or disabled. For more details, refer to

register field enc_8b10b_dis in Table A. 32.

When enabled, MPCS module soft resets the RX path (not including the register space).

For more details, refer to register field rx_mpcs_rst in Table A. 34.

RX Phase Compensation FIFO

Specifies whether the RX phase compensation FIFO is enabled or disabled. For more

details, refer to register field rx_fifo_dis in Table A. 34.

Specifies whether the 8b10b decoding is enabled or disabled. For more details, refer to

register field dec_8b10b_dis in Table A. 34.

Specifies whether the Word Alignment is enabled or not. For more details, refer to

register field wa_dis in Table A. 37.

Put the COMMA byte to LSByte

Specifies the value of reg20. rfifo_com_align.

Specifies the use of automatic word alignment or use of manual alignment. For more

details, refer to register field auto_wa_dis in Table A. 37.

Primary Word Alignment Pattern

Value

Primary Pattern Value in hex form. For more details, refer to register field pri_wa_ptn in

Table A. 38 to Table A. 40.

Specifies whether the Secondary Word Alignment Pattern Matching is enabled or not.

For more details, refer to register field sec_waptn_dis in Table A. 37.

Secondary Word Alignment Pattern

Value

Secondary Pattern Value in hex form. For more details, refer to register field pri_wa_ptn

in Table A. 41 to Table A. 43.

Use LSByte of the Word Alignment

Specifies whether to put the LSByte of the word alignment pattern to [9:0] of the data

bus or not. For more details, refer to register field align_2byte_dis in Table A. 37.

Specifies whether to use sync_det FSM to control the automatic word alignment. For

more details, refer to register field syncdet_fsm_dis in Table A. 37.

Number of Valid Sync Code Groups

The number of valid synchronization code groups or ordered sets in decimal form that

“sync_det” FSM must receive to achieve synchronization state.

Number of Bad Code Groups

The number of bad code groups in decimal form received by “sync_det” FSM to conclude

the loss of synchronization.

Number of Good Code Groups

The number of continuous good code in decimal form groups received by “sync_det”

FSM to reduce the error count by one.

Specifies the whether the Clock Compensation FIFO is enabled or not.

Enable and use mpcs/epcs_cc_clk_i.

Specifies the length of sync_det pattern.

Specifies whether the Sync Pattern is enabled or disabled.

Specifies the pattern code for sync_det.

Specifies whether the Secondary Sync Pattern is enabled or disabled.

Primary Sync_det Pattern Byte 0

Specifies the primary pattern Byte 0 in hex form for Sync_det.

Primary Sync_det Pattern Byte 1

Specifies the primary pattern Byte 1 in hex form for Sync_det.

Primary Sync_det Pattern Byte 2

Specifies the primary pattern Byte 2 in hex form for Sync_det.

Primary Sync_det Pattern Byte 3

Specifies the primary pattern Byte 3 in hex form for Sync_det.

Secondary Sync_det Pattern Byte 0

Specifies the secondary pattern Byte 0 in hex form for Sync_det.

Secondary Sync_det Pattern Byte 1

Specifies the secondary pattern Byte 0 in hex form for Sync_det.

Secondary Sync_det Pattern Byte 2

Specifies the secondary pattern Byte 0 in hex form for Sync_det.

Secondary Sync_det Pattern Byte 3

Specifies the secondary pattern Byte 0 in hex form for Sync_det.

Specifies whether the Lane Alignment is enabled or not.

Specifies the code mode of the input data. For more details, refer to register field

lalign_10b in Table A. 67.

Lane Alignment Pattern Length

Specifies the lane alignment pattern length in byte. For more details, refer to register

Loading...

Loading...