CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

114 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

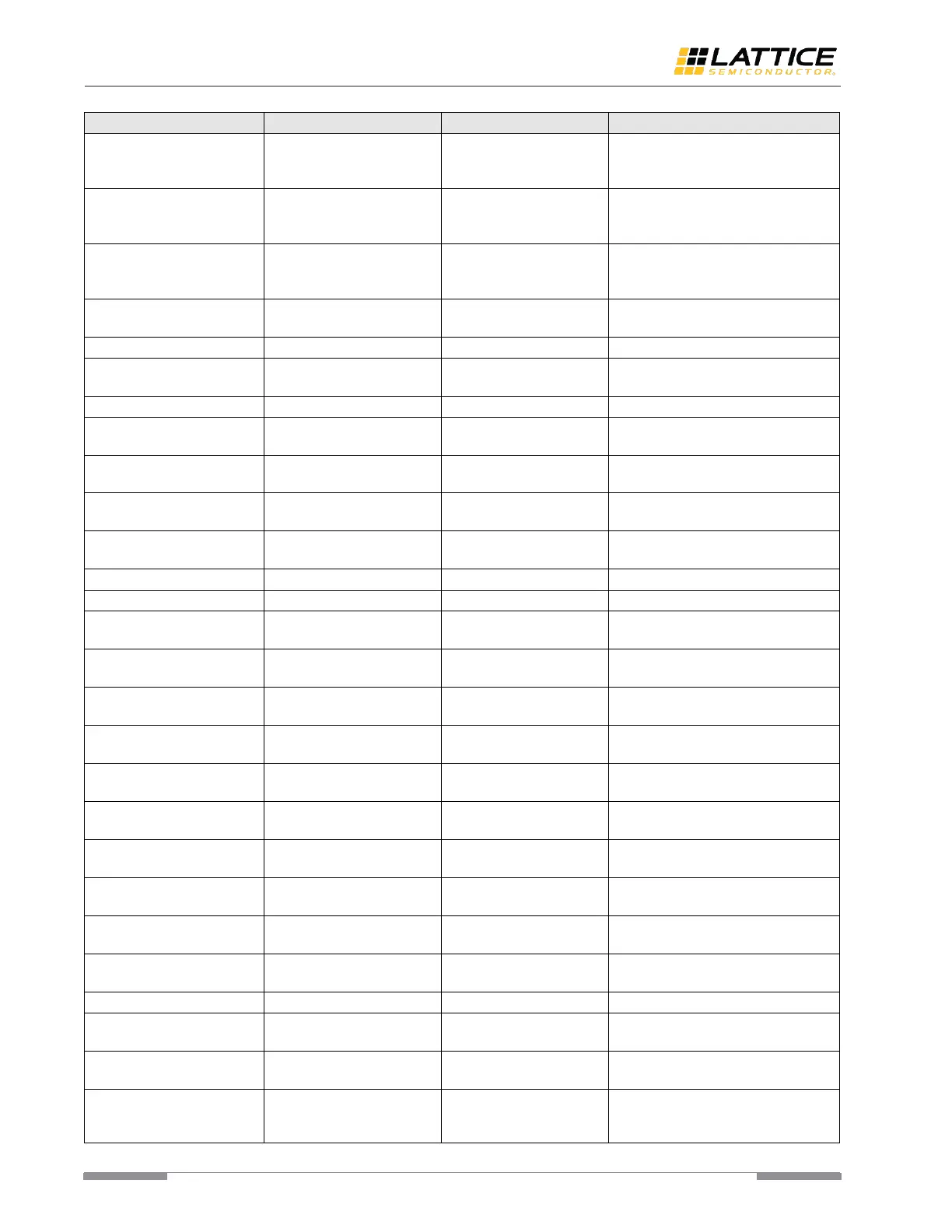

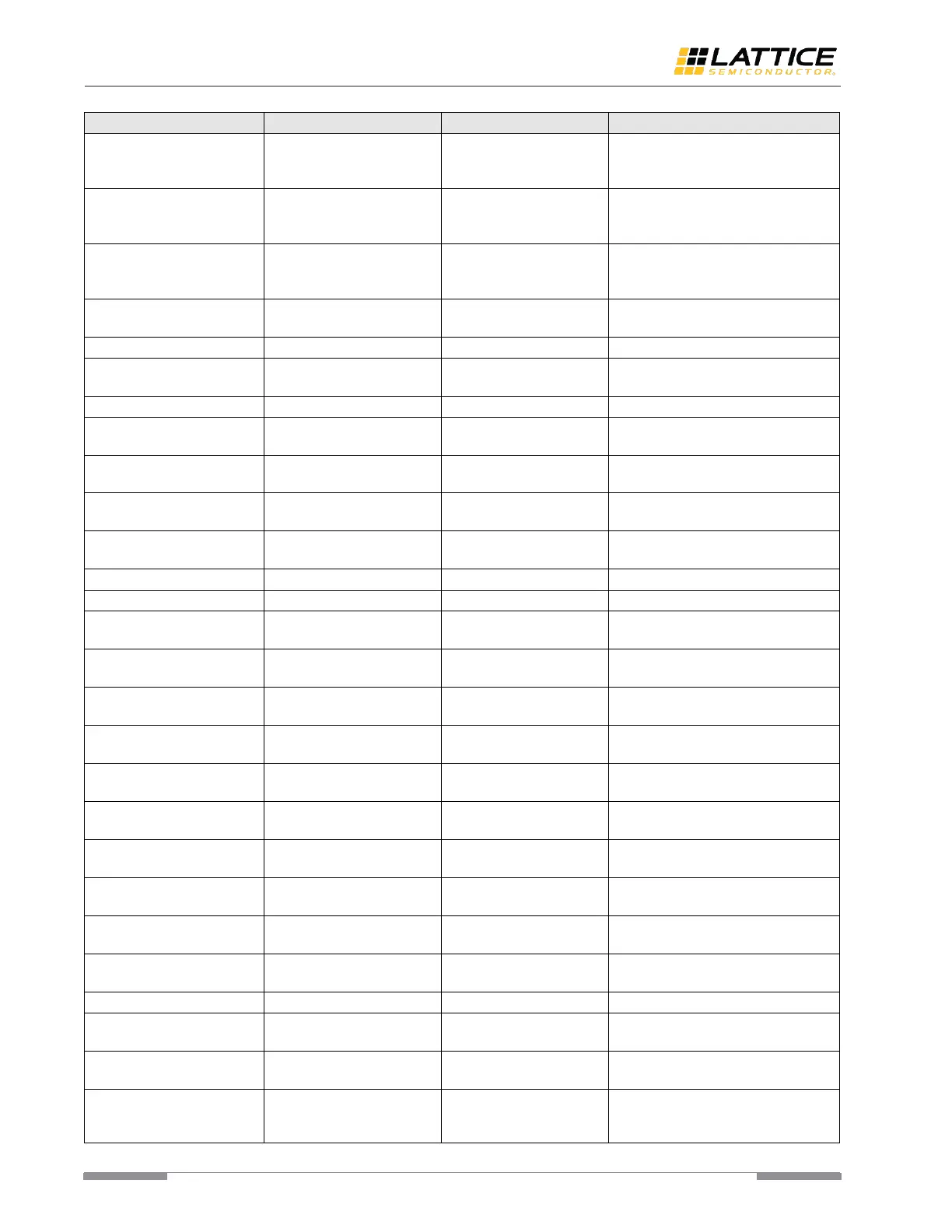

Dependency on Other Attributes

Number of Valid Sync Code

Groups

Active if (Word Alignment ==

“ENABLED”) and (Use ‘sync_det’ FSM

== “ENABLED”)

Number of Bad Code

Groups

Active if (Word Alignment ==

“ENABLED”) and (Use ‘sync_det’ FSM

== “ENABLED”)

Number of Good Code

Groups

Active if (Word Alignment ==

“ENABLED”) and (Use ‘sync_det’ FSM

== “ENABLED”)

Clock Frequency

Compensation

Active if Enable CTC FIFO ==

“ENABLED”

Primary Skip Pattern Byte 0

(HEX)

Primary Skip Pattern Byte 1

(HEX)

Primary Skip Pattern Byte 2

(HEX)

Primary Skip Pattern Byte 3

(HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Active if Sync Pattern Alignment ==

“ENABLED”

Primary Sync_det Pattern

Byte 0 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Primary Sync_det Pattern

Byte 1 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Primary Sync_det Pattern

Byte 2 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Primary Sync_det Pattern

Byte 3 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Secondary Sync_det Pattern

Byte 0 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Secondary Sync_det Pattern

Byte 1 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Secondary Sync_det Pattern

Byte 2 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Secondary Sync_det Pattern

Byte 3 (HEX)

Active if Sync Pattern Alignment ==

“ENABLED”

Active if Lane Alignment ==

“ENABLED”

“1_BYTE”, “2_BYTE”,

“4_BYE”

Active if Lane Alignment ==

“ENABLED”

Maximum Lane-to-Lane

Skew

“NO_SKEW”, “1_SKEW”,

“2_SKEW”, “3_SKEW”,

“4_SKEW”, “5_SKEW”,

Active if Lane Alignment ==

“ENABLED”

Loading...

Loading...