CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

40 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

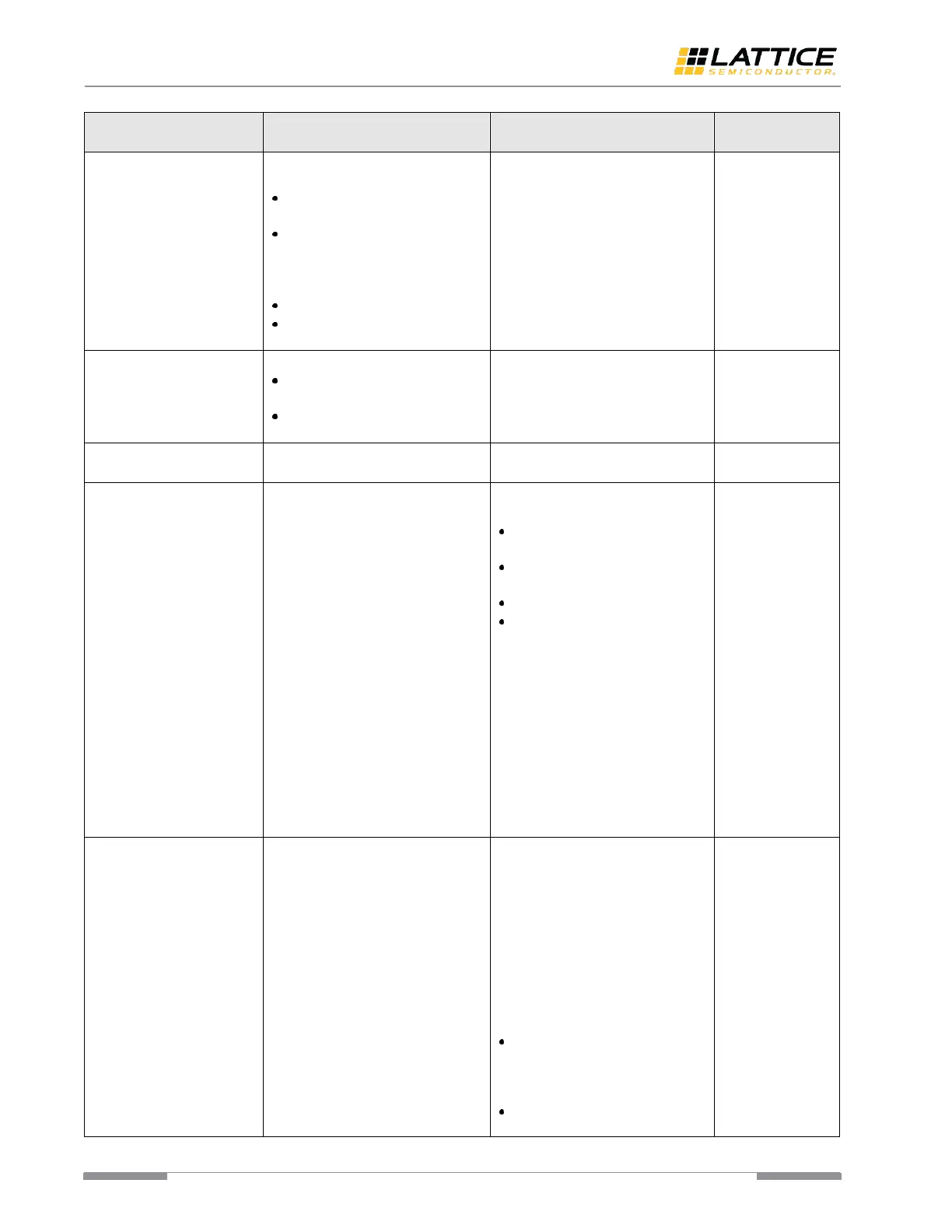

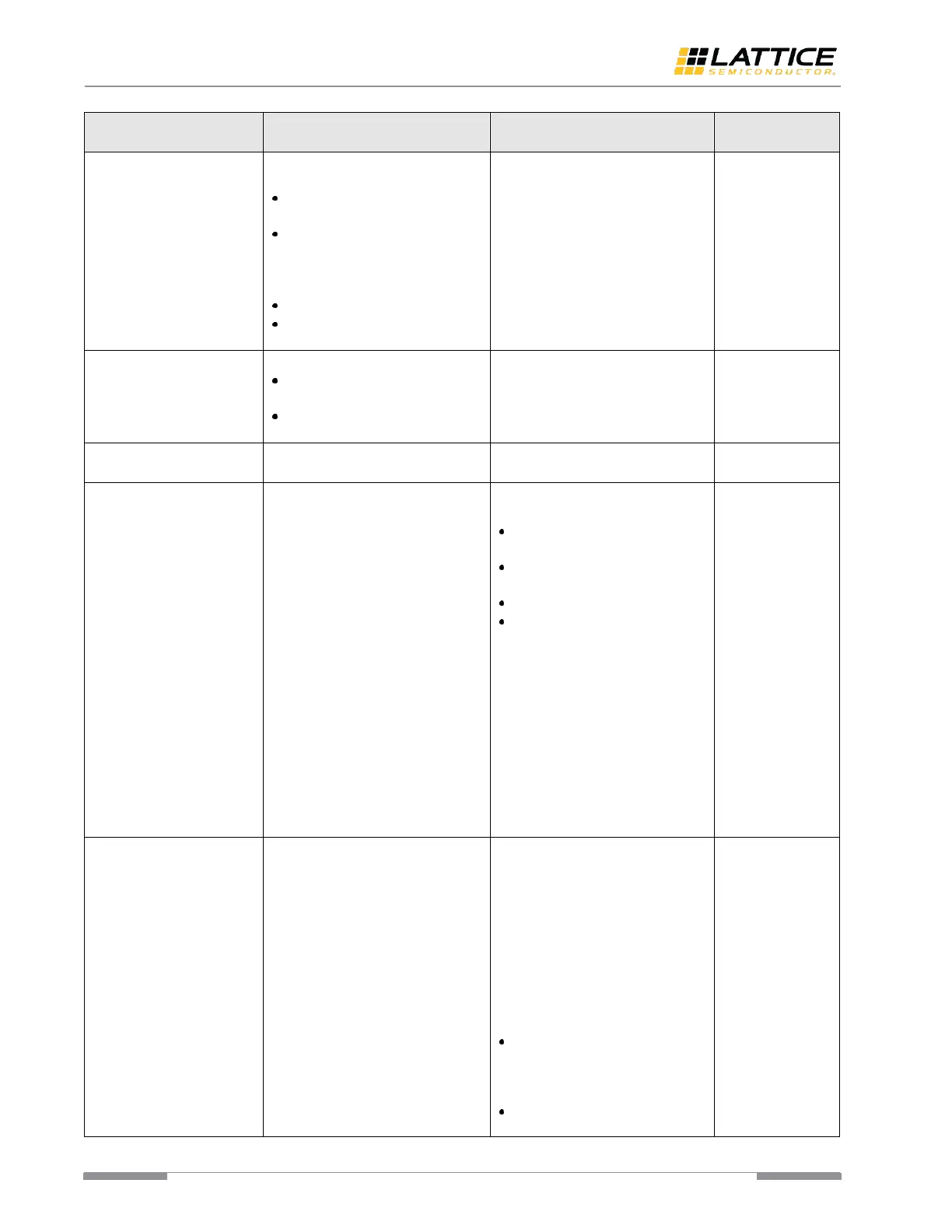

MPCS Mode

Protocol != “10GE”

MPCS Mode

Protocol == “10GE”

this signal indicates the forced

running disparity:

1: force positive running

disparity.

0: force negative running

disparity.

If not in “force running disparity”

mode):

1: revert running disparity.

0: use running disparity

calculated by 8B/10B encoder.

mpcs_tx_ch_din_i[51:48]/

epcs_txdata_i[51:48]

tx_frcdata[3:0]

1: force 8B/10B encoder to

output “tx_data”.

0: do not force the outputted

data of 8B/10B encoder.

tx_data_64b[51:48]

Input data.

mpcs_tx_ch_din_i[63:52]/

epcs_txdata_i[63:52]

tx_data_64b[63:52]

Input data.

mpcs_tx_ch_din_i[71:64]/

epcs_txdata_i[71:64]

tx_control[7:0]/ tx_header[1:0]

8-bit control indication

bit[0] is the control signal for

tx_data_64b[7:0].

bit[1] is the control signal for

tx_data_64b[15:8].

…

bit[7] is the control signal for

tx_data_64b[63:56].

bit[1:0] of this signal can also be

used as 2-bit block header. If "force

data" signal is asserted ("tx_frcpkt"

is driven high), or if 64B/66B

encoder is bypassed, bit[1:0] of this

signal, along with the 64-bit payload

(coming from "tx_data_64b"), forms

a 66-bit block which is usually

generated by the Encoder. In this

case, bit[7:2] of this signal are

unused.

mpcs_tx_ch_din_i[72]/

epcs_txdata_i[72]

tx_frcpkt

When this signal is asserted high,

the 64-bit data (tx_data_64b) and

2-bit header (tx_control[1:0]) on the

same clock cycle is used to drive TX

Gear Box directly. The Encoder and

Scrambler are bypassed in this case.

Once de-asserted, the 64-bit data

and 8-bit control are encoded and

scrambled before they go to TX

Gear Box.

1'b1: on the same cycle, use

64-bit data and 2-bit header

coming from user logic to feed

the Gear Box.

1'b0: process the 64-bit data and

8-bit control as normal (go

Loading...

Loading...