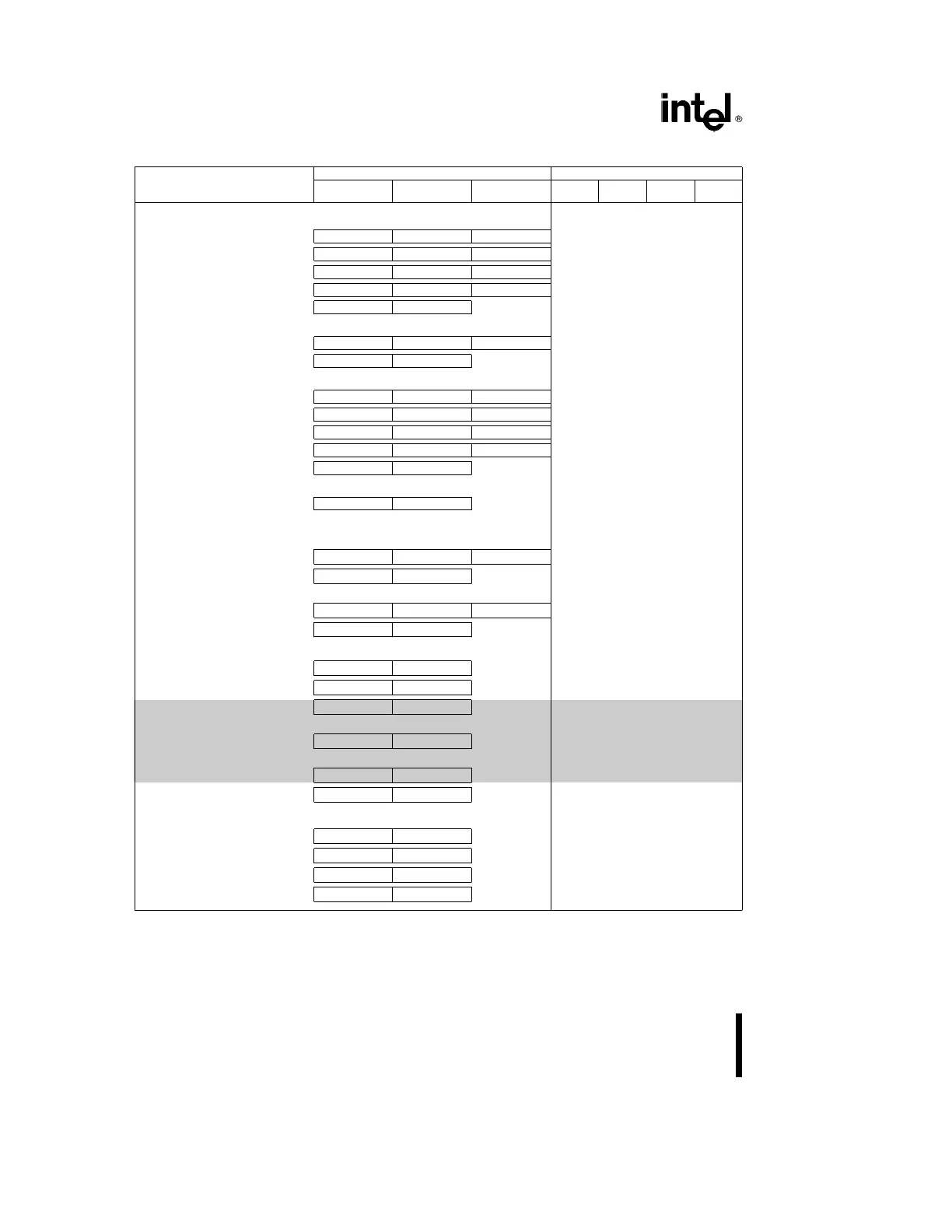

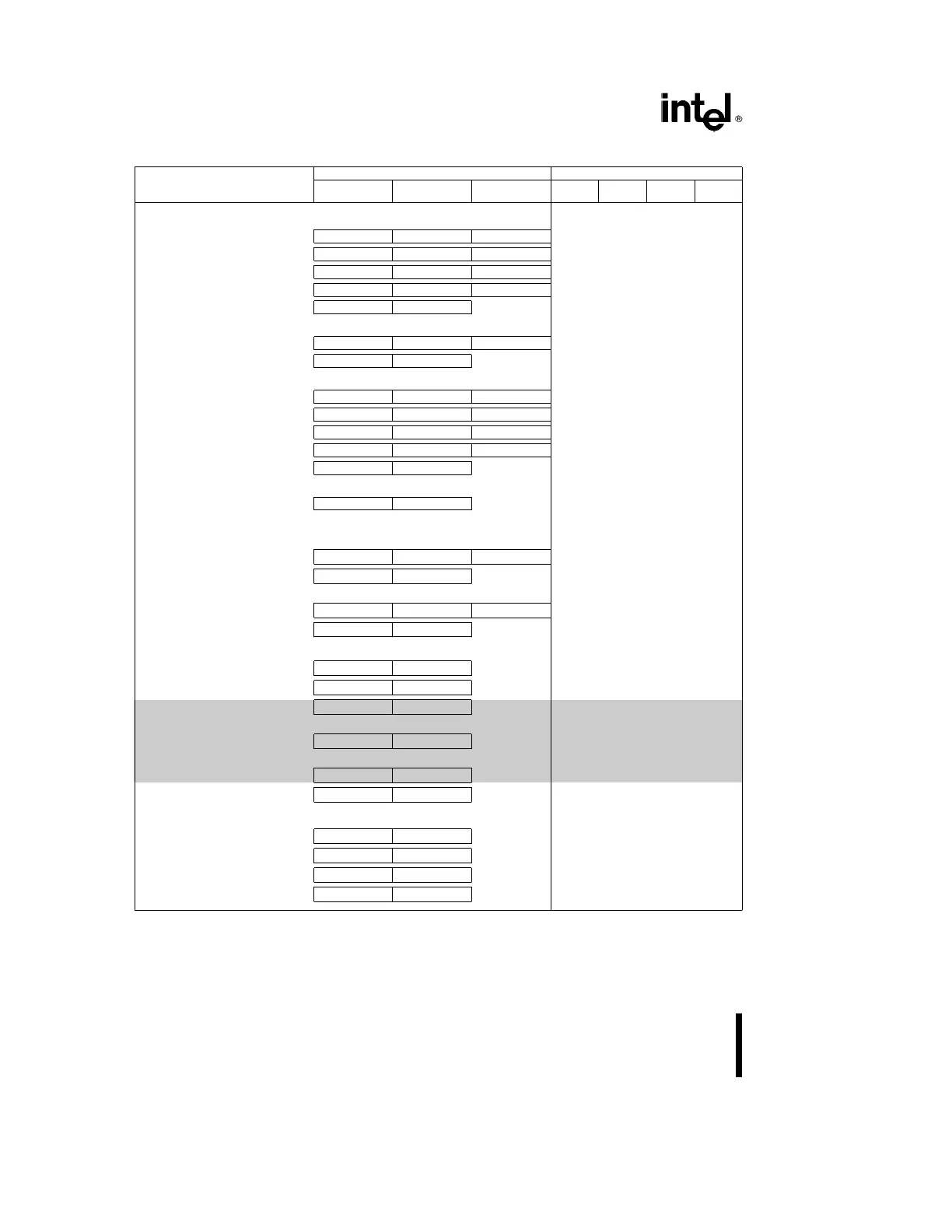

80C187

80C187 Extensions to the 80C186 Instruction Set

Encoding Clock Count Range

Instruction Byte Byte Optional 32-Bit 32-Bit 64-Bit 16-Bit

0 1 Bytes 2 – 3 Real Integer Real Integer

DATA TRANSFER

FLD

e

Load

a

Integer/real memory to ST(0) ESC MF 1 MOD 000 R/M DISP 40 65–72 59 67 –71

Long integer memory to ST(0) ESC 111 MOD 101 R/M DISP 90 – 101

Extended real memory to ST(0) ESC 011 MOD 101 R/M DISP 74

BCD memory to ST(0) ESC 111 MOD 100 R/M DISP 296 –305

ST(i) to ST(0) ESC 001 11000 ST(i) 16

FST

e

Store

ST(0) to integer/real memory ESC MF 1 MOD 010 R/M DISP 58 93–107 73 80–93

ST(0) to ST(i) ESC 101 11010 ST(i) 13

FSTP

e

Store and Pop

ST(0) to integer/real memory ESC MF 1 MOD 011 R/M DISP 58 93–107 73 80–93

ST(0) to long integer memory ESC 111 MOD 111 R/M DISP 116–133

ST(0) to extended real ESC 011 MOD 111 R/M DISP 83

ST(0) to BCD memory ESC 111 MOD 110 R/M DISP 542 –564

ST(0) to ST(i) ESC 101 11001 ST (i) 14

FXCH

e

Exchange

ST(i) and ST(0) ESC 001 11001 ST(i) 20

COMPARISON

FCOM

e

Compare

Integer/real memory to ST(0) ESC MF 0 MOD 010 R/M DISP 48 78–85 67 77 –81

ST(i) to ST(0) ESC 000 11010 ST(i) 26

FCOMP

e

Compare and pop

Integer/real memory to ST ESC MF 0 MOD 011 R/M DISP 48 78–85 67 77–81

ST(i) to ST(0) ESC 000 11011 ST(i) 28

FCOMPP

e

Compare and pop twice

ST(1) to ST(0) ESC 110 1101 1001 28

FTST

e

Test ST(0) ESC 001 1110 0100 30

FUCOM

e

Unordered compare ESC 101 11100 ST(i) 26

FUCOMP

e

Unordered compare

and pop

ESC 101 11101 ST(i) 28

FUCOMPP

e

Unordered compare

and pop twice

ESC 010 1110 1001 28

FXAM

e

Examine ST(0) ESC 001 11100101 32-40

CONSTANTS

FLDZ

e

Load

a

0.0 into ST(0) ESC 001 1110 1110 22

FLD1

e

Load

a

1.0 into ST(0) ESC 001 1110 1000 26

FLDPI

e

Load pi into ST(0) ESC 001 1110 1011 42

FLDL2T

e

Load log

2

(10) into ST(0) ESC 001 1110 1001 42

Shaded areas indicate instructions not available in 8087.

NOTE:

a. When loading single- or double-precision zero from memory, add 5 clocks.

28

Loading...

Loading...