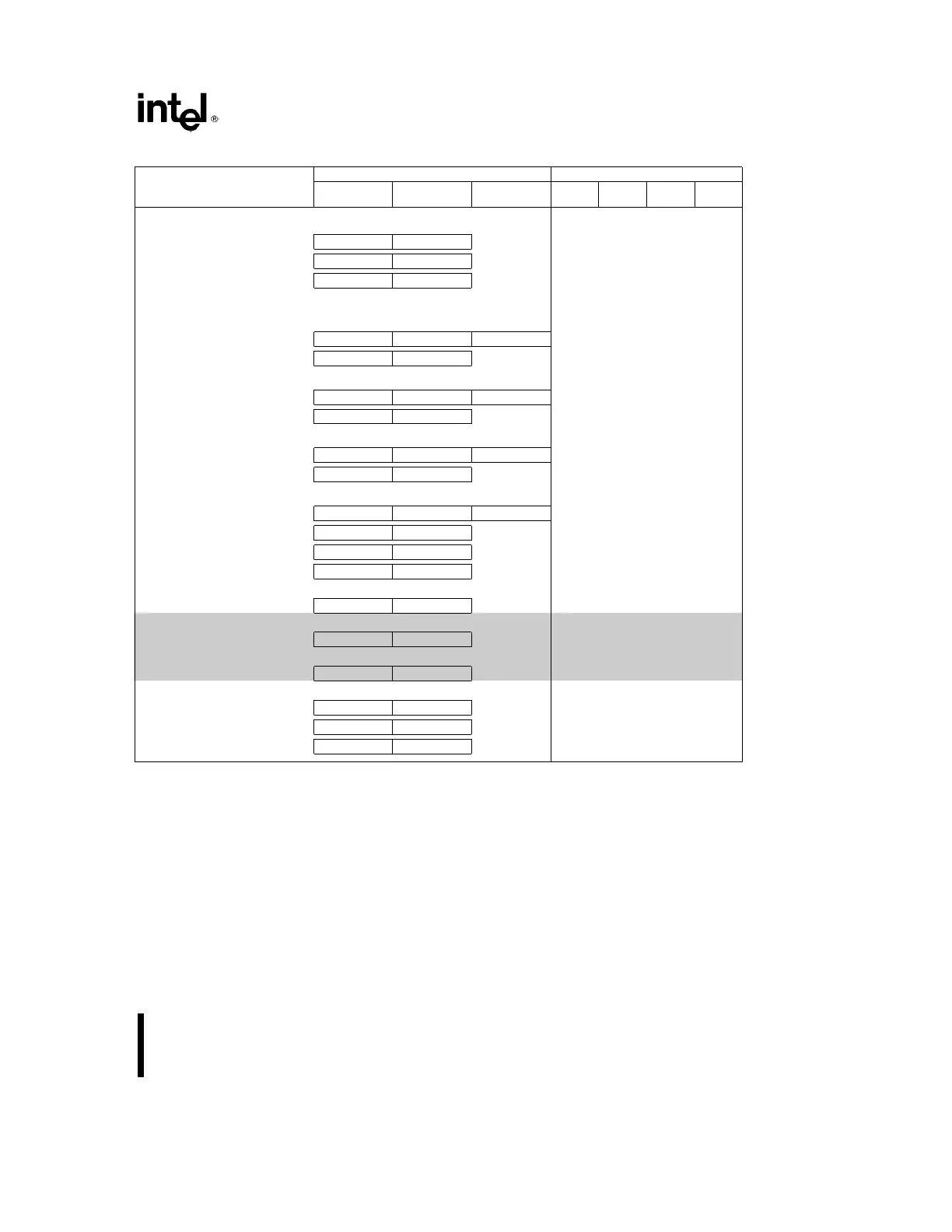

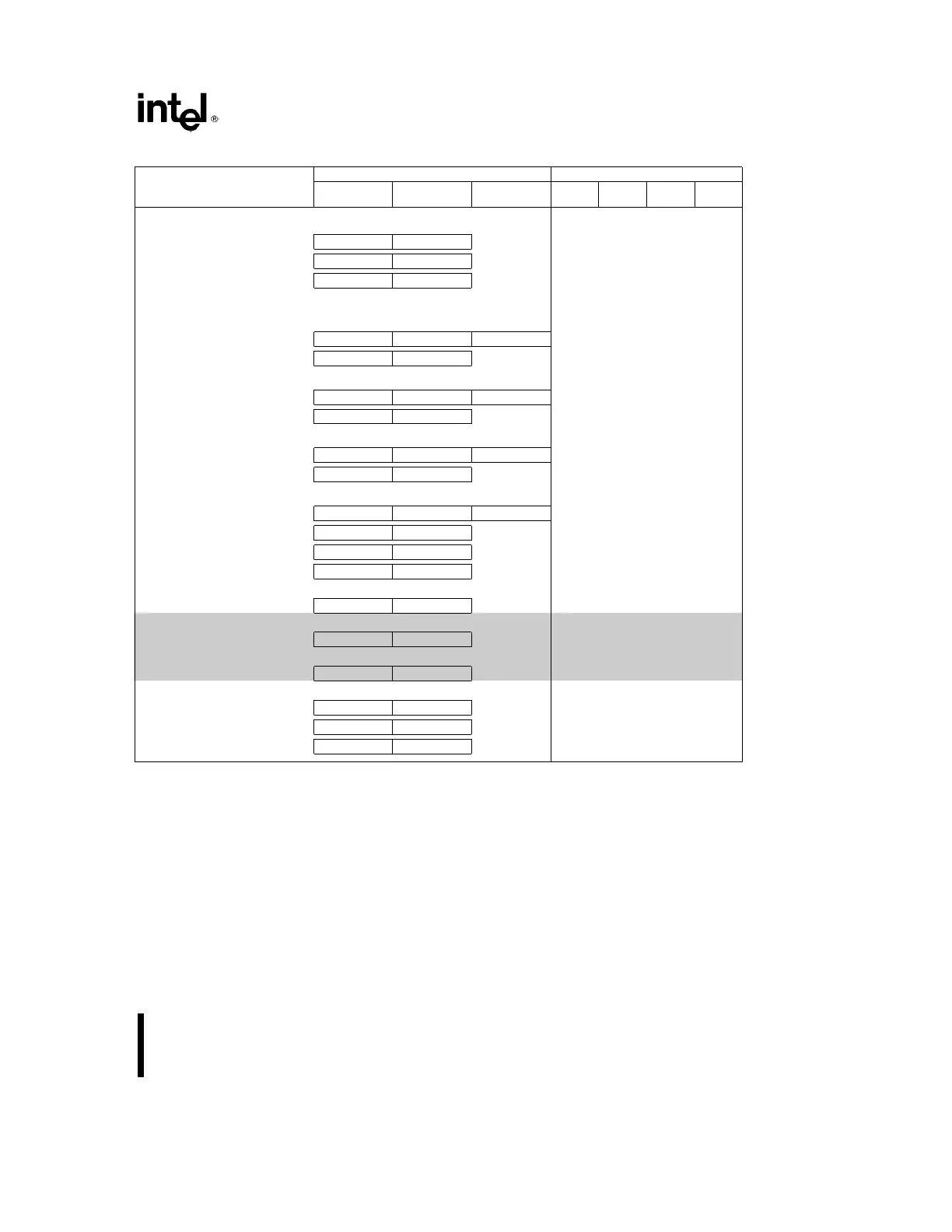

80C187

80C187 Extensions to the 80C186 Instruction Set (Continued)

Encoding Clock Count Range

Instruction Byte Byte Optional 32-Bit 32-Bit 64-Bit 16-Bit

0 1 Bytes 2 – 3 Real Integer Real Integer

CONSTANTS (Continued)

FLDL2E

e

Load log

2

(e) into ST(0) ESC 001 1110 1010 42

FLDLG2

e

Load log

10

(2) into ST(0) ESC 001 1110 1100 43

FLDLN2

e

Load log

e

(2) into ST(0) ESC 001 1110 1101 43

ARITHMETIC

FADD

e

Add

Integer/real memory with ST(0) ESC MF 0 MOD 000 R/M DISP 44–52 77–92 65–73 77–91

ST(i) and ST(0) ESCdP0 11000 ST(i) 25–33

b

FSUB

e

Subtract

Integer/real memory with ST(0) ESC MF 0 MOD 10 R R/M DISP 44–52 77–92 65– 73 77–91

c

ST(i) and ST(0) ESCdP0 1110 R R/M 28–36

d

FMUL

e

Multiply

Integer/real memory with ST(0) ESC MF 0 MOD 001 R/M DISP 47–57 81–102 68–93 82–93

ST(i) and ST(0) ESCdP0 1100 1 R/M 31–59

e

FDIV

e

Divide

Integer/real memory with ST(0) ESC MF 0 MOD 11 R R/M DISP 108 140–147

f

128 142 – 146

g

ST(i) and ST(0) ESCdP0 1111 R R/M 90

h

FSQRT

i

e

Square root ESC 001 1111 1010 124–131

FSCALE

e

Scale ST(0) by ST(1) ESC 001 1111 1101 69–88

FPREM

e

Partial remainder of

ST(0)

d

ST(1) ESC 001 1111 1000 76–157

FPREM1

e

Partial remainder

(IEEE)

ESC 001 1111 0101 97–187

FRNDINT

e

Round ST(0)

to integer

ESC 001 1111 1100 68–82

FXTRACT

e

Extract components

of ST(0)

ESC 001 1111 0100 72–78

FABS

e

Absolute value of ST(0) ESC 001 1110 0001 24

FCHS

e

Change sign of ST(0) ESC 001 1110 0000 26 – 27

Shaded areas indicate instructions not available in 8087.

NOTES:

b. Add 3 clocks to the range when d

e

1.

c. Add 1 clock to each range when R

e

1.

d. Add 3 clocks to the range when d

e

0.

e. typical

e

54 (When d

e

0, 48 – 56, typical

e

51).

f. Add 1 clock to the range when R

e

1.

g. 153 – 159 when R

e

1.

h. Add 3 clocks to the range when d

e

1.

i.

b

0

s

ST(0)

s

a %

.

29

Loading...

Loading...