122 b EDN S

EPTEMBER 24, 1998

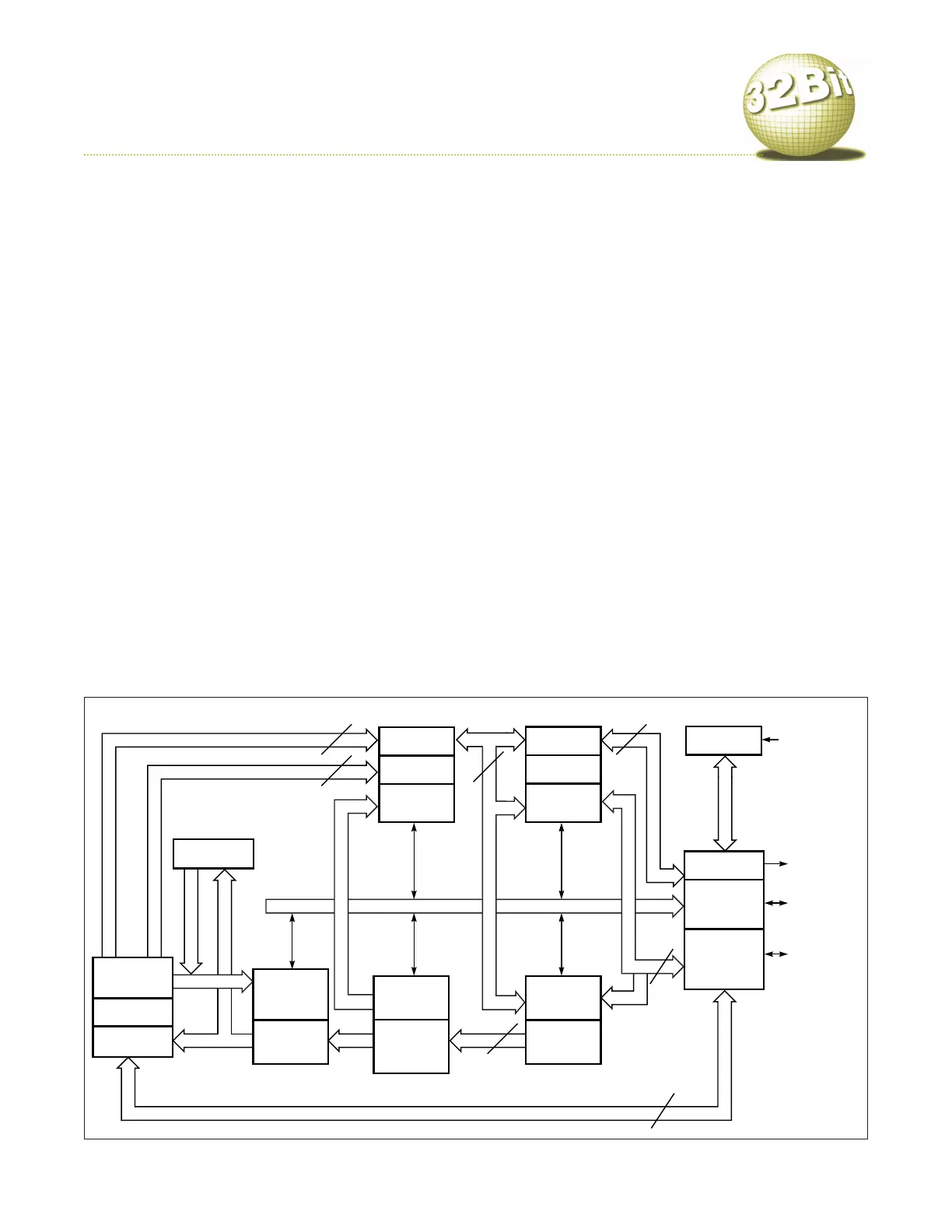

The 386 has disappeared from the desktop-PC market but has

developed a strong presence in embedded-PC applications.

Register-based, the 80386 architecture has four general-pur-

pose registers, four index/pointer registers, six 16-bit segment

registers, and two 32-bit status and control registers. Intel’s

8086 designers used 64-kbyte segments to extend addressing

to 1 Mbyte. The 80386 also uses segmentation; however,

because the general-purpose and index/pointer registers are

now 32 bits, the segment limits extend to the full 4-Gbyte

addressing range, and a segment register references a segment

descriptor with a 32-bit base address. These descriptors also

carry addressing-range and protection limits to prevent data

accesses into code, data that executes as code, and access to

inner privilege levels by outer levels.

Hardware-descriptor registers hold segment-access rights

and segment-base address and size limits. In protected-mode

addressing, a 16-bit selector points to a segment descriptor

and furnishes a base address. The base address adds to the 32-

bit effective address, producing a 32-bit linear address, which

the 80386 then uses as a physical or linear-page address.

The 386 has four code/data breakpoint registers and two

control registers for debugging. You can set the breakpoint

registers with addresses for halting execution on a program

or data access.

Power management: System-management mode (SMM), a

power-management mechanism, enables code to control

CPU power without rewriting or revamping operating soft-

ware. The CPU enters SMM via a hardware interrupt, the sys-

tem-management interrupt (SMI); the SMI code can set

SMMs to reduce chip power dissipation. Integrated versions

of the 386, including Intel’s 386EX, have idle and power-

down modes: Idle discontinues CPU processing but keeps

peripherals active, and power-down shuts down the entire

chip. AMD’s 386SC300 chip has low-speed mode, during

which the CPU goes to 0.5 MHz; doze, which stops the CPU,

system, and DMA clocks; sleep, which stops additional clocks

and peripherals; and suspend, which stops everything except

the real-time clock and memory.

Special instructions: The 386 instruction set is a superset of

the 8086/186. To support SMM, the 386 has seven addition-

al instructions, such as RSM (resume), which causes the

processor to resume from SMM.

Special on-chip peripherals: Intel’s 386EX peripherals

include a serial-I/O unit, a chip select, a clock generator, a

DMA- and bus-arbitrator unit, a DRAM-refresh-control unit,

an interrupt-control unit, a memory-management unit, and

a parallel-I/O unit. AMD’s ElanSC300 combines an Am386

CPU with a PC/A

T chip set and essential embedded-PC

peripherals. The ElanSC300 also includes mobile-computing

peripherals, such as PLL clock generators, PCMCIA-card sup-

port, LCD-graphics control, a memory controller, DMA and

interrupt controllers, a real-time clock, a serial port, and a par-

allel port.

Development tools: Numerous third-party vendors support

the 386 architecture. They provide tools that include assem-

blers, compilers, linkers/locators, remote software debuggers,

software simulators, and integrated design environments for

software development. In addition, several vendors provide

utilities, such as flash-programming, device-driver, and flash-

translation-layer implementations. Hardware tools include

in-circuit emulators, logic analyzers, evaluation platforms,

and single-board computers. Operating-system support

includes DOS and windowed OSs and a variety of real-time

OSs from small, royalty-free microkernels to feature-rich

graphical-user-interface RTOSs.

80386

Loading...

Loading...