8254

231164–9

NOTE:

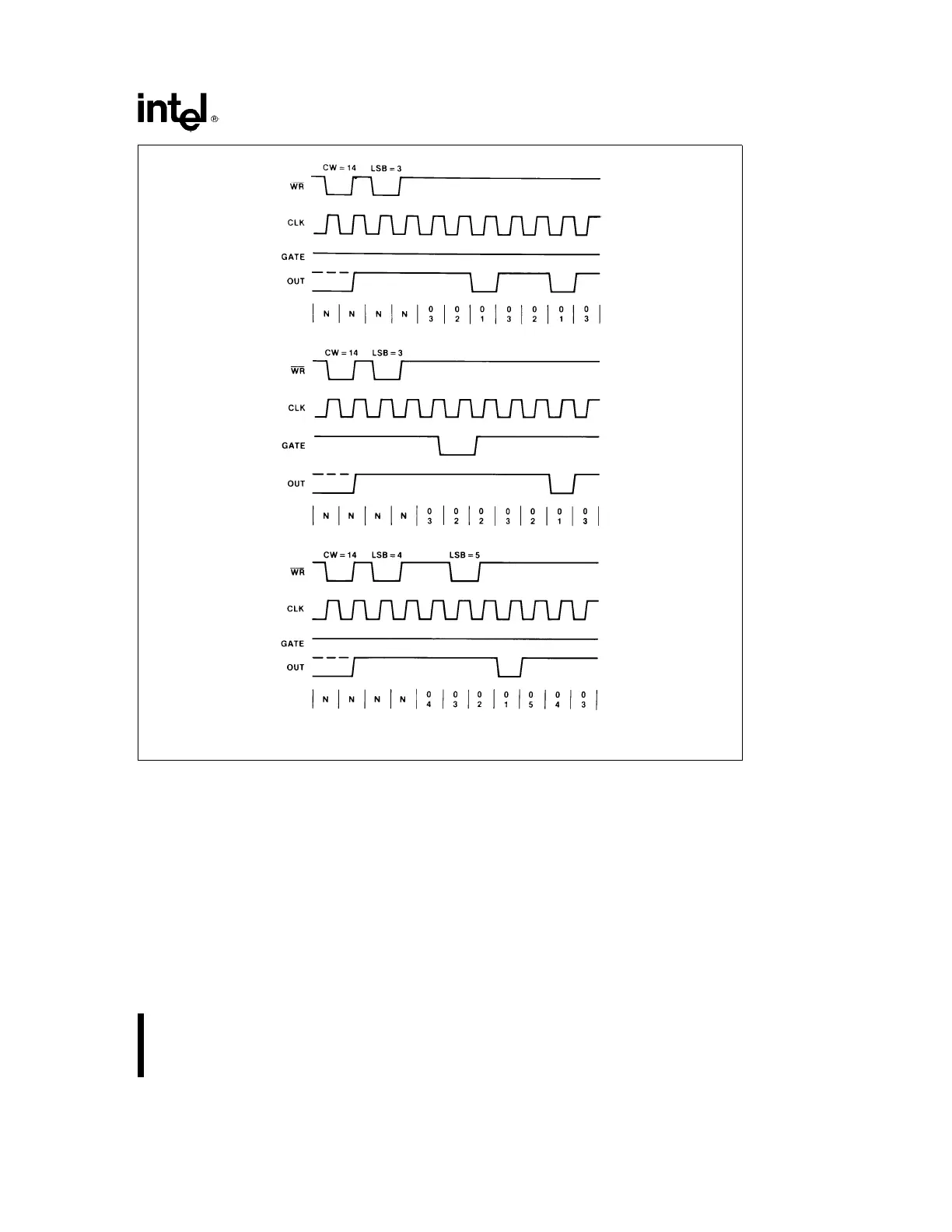

A GATE transition should not occur one clock prior to terminal count.

Figure 17. Mode 2

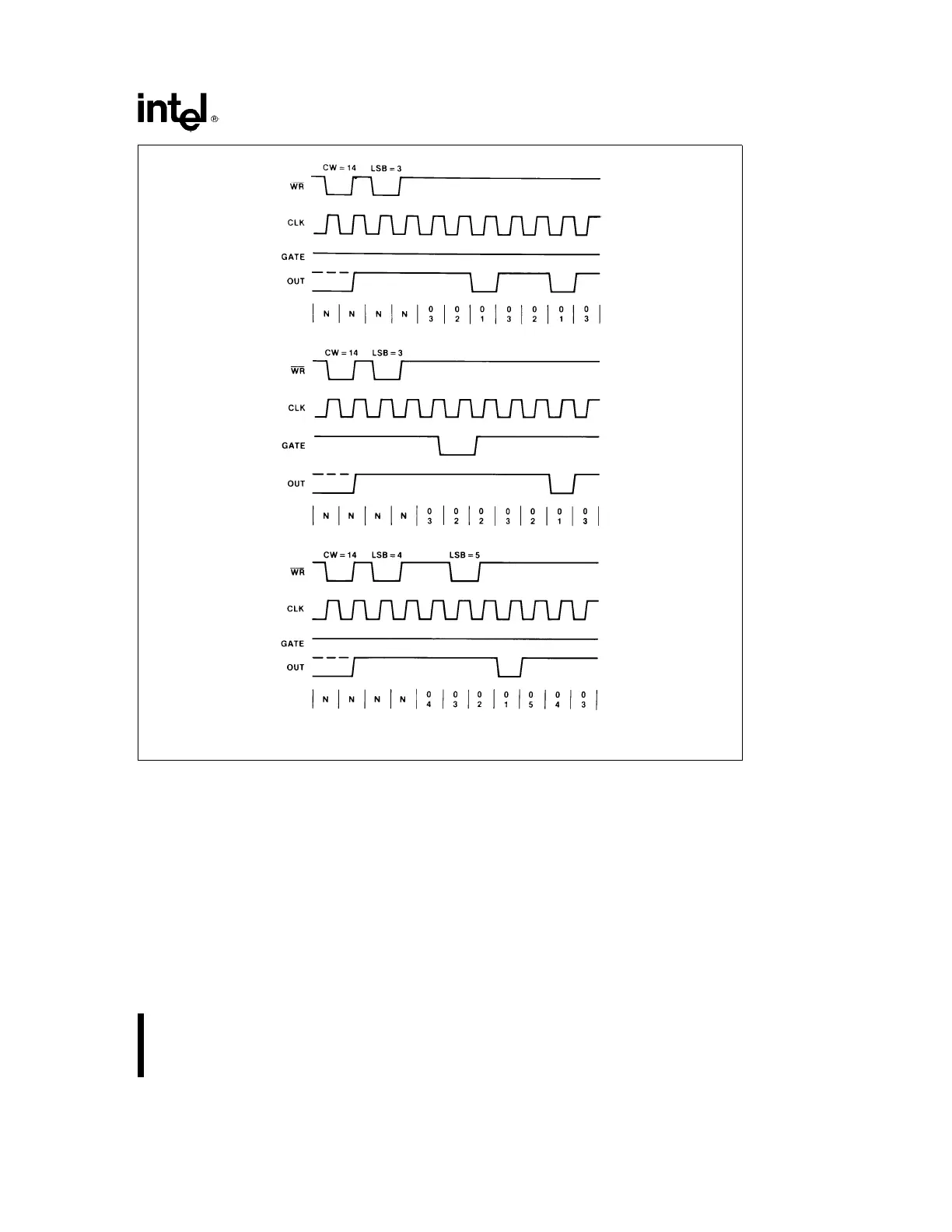

new count. Otherwise, the new count will be loaded

at the end of the current half-cycle.

Mode 3 is implemented as follows:

Even counts: OUT is initially high. The initial count is

loaded on one CLK pulse and then is decremented

by two on succeeding CLK pulses. When the count

expires OUT changes value and the Counter is re-

loaded with the initial count. The above process is

repeated indefinitely.

Odd counts: OUT is initially high. The initial count

minus one (an even number) is loaded on one CLK

pulse and then is decremented by two on succeed-

ing CLK pulses. One CLK pulse

after

the count ex-

pires, OUT goes low and the Counter is reloaded

with the initial count minus one. Succeeding CLK

pulses decrement the count by two. When the count

expires, OUT goes high again and the Counter is

reloaded with the initial count minus one. The above

process is repeated indefinitely. So for odd counts,

OUT will be high for (N

a

1)/2 counts and low for

(N

b

1)/2 counts.

13

Loading...

Loading...