8254

231164–8

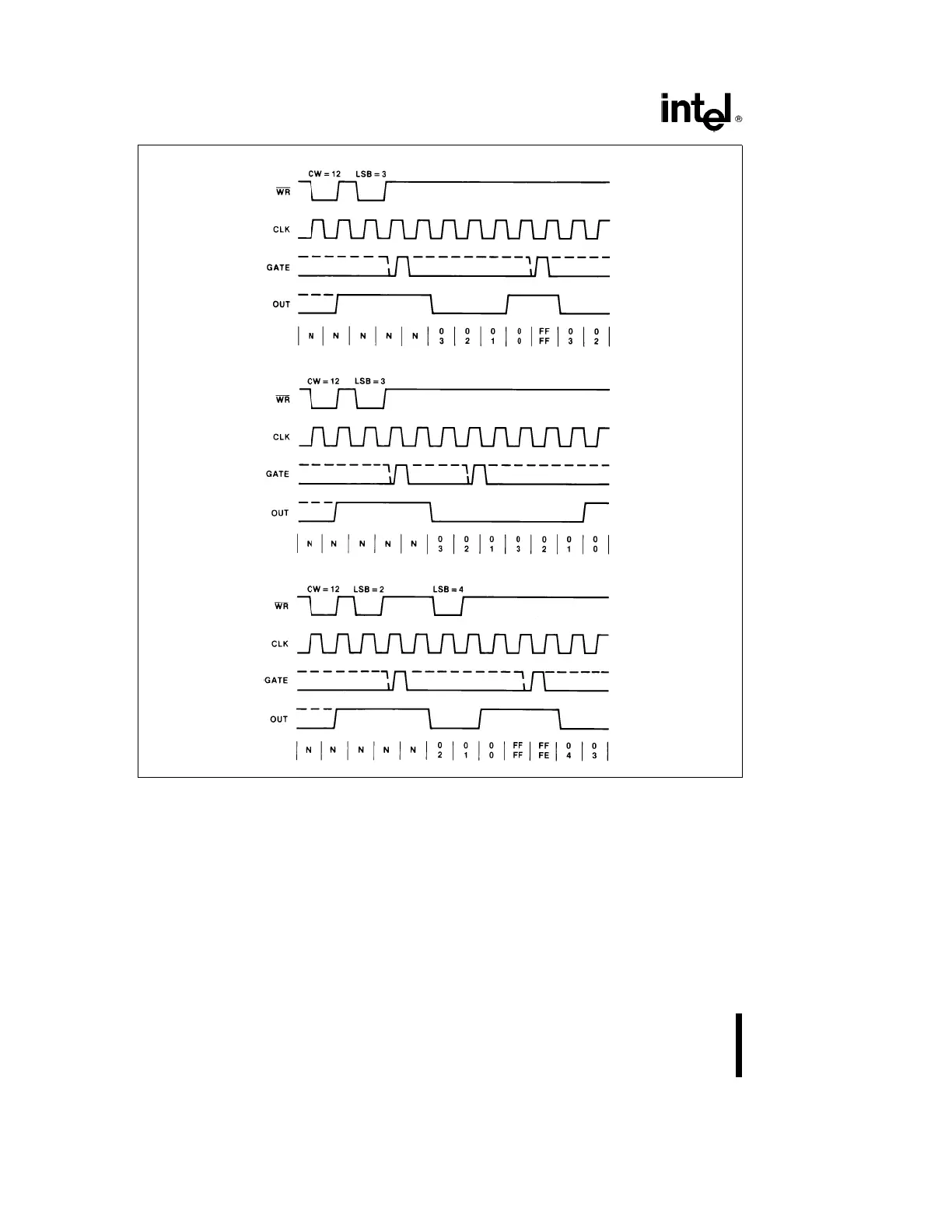

Figure 16. Mode 1

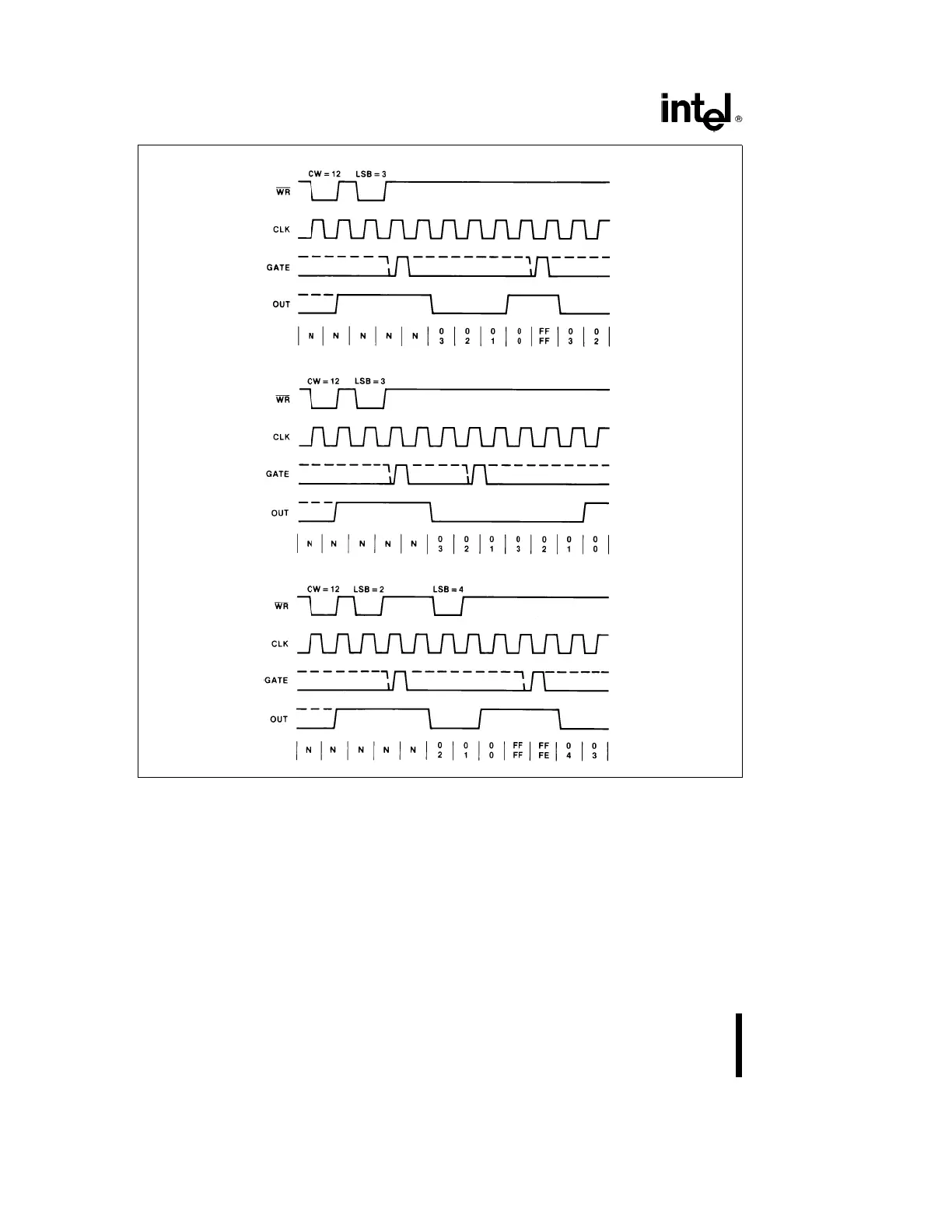

initial count has expired, OUT goes low for the re-

mainder of the count. Mode 3 is periodic; the se-

quence above is repeated indefinitely. An initial

count of N results in a square wave with a period of

N CLK cycles.

GATE

e

1 enables counting; GATE

e

0 disables

counting. If GATE goes low while OUT is low, OUT is

set high immediately; no CLK pulse is required. A

trigger reloads the Counter with the initial count on

the next CLK pulse. Thus the GATE input can be

used to synchronize the Counter.

After writing a Control Word and initial count, the

Counter will be loaded on the next CLK pulse. This

allows the Counter to be synchronized by software

also.

Writing a new count while counting does not affect

the current counting sequence. If a trigger is re-

ceived after writing a new count but before the end

of the current half-cycle of the square wave, the

Counter will be loaded with the new count on the

next CLK pulse and counting will continue from the

12

Loading...

Loading...