126 b EDN S

EPTEMBER 24, 1998

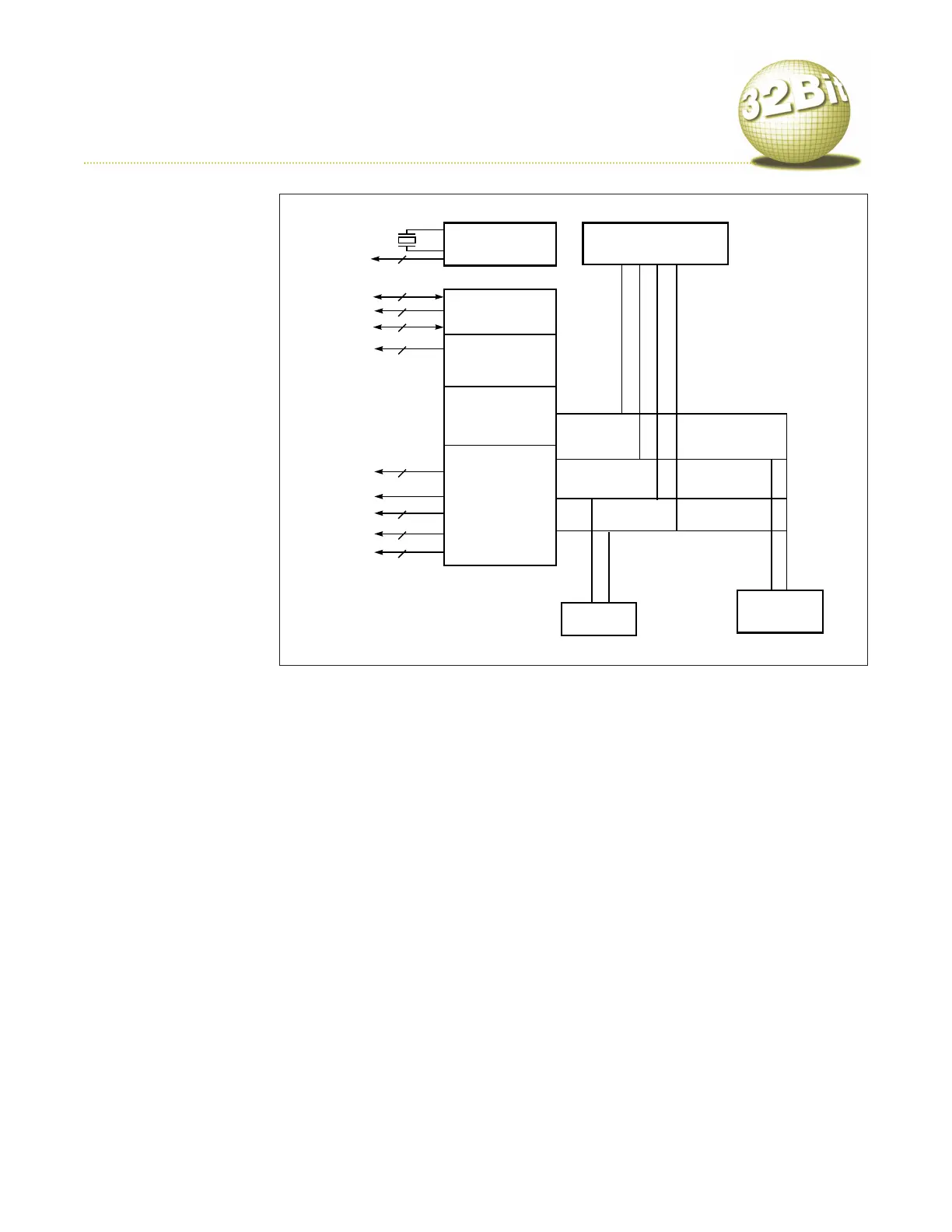

Fujitsu based its MB8683x,

or SPARClite, family on V8E

spec, SPARC International’s

(www.sparc.com) embed-

ded specification. The fami-

ly features a 32-bit ALU and

uses a load/store architec-

ture with a register stack of

136 32-bit registers. (The

86933H chips have 104.)

Eight reserved registers hold

global values. The remain-

ing registers arrange into

eight overlapping register

windows, one for each sub-

routine. This setup speeds

procedure calls and inter-

rupt processing. Multiple

contexts can be present

concurrently by limiting

the number of registers for a

task.

Fujitsu engineers extend-

ed the SPARC pipeline for

the SPARClite family to

fetch, decode, execute,

memory, and write-back

stages. The memory stage

minimizes the effects of

load/store operations and

reduces a load/store to one-

cycle execution. The stage is

idle for nonload/store operations.

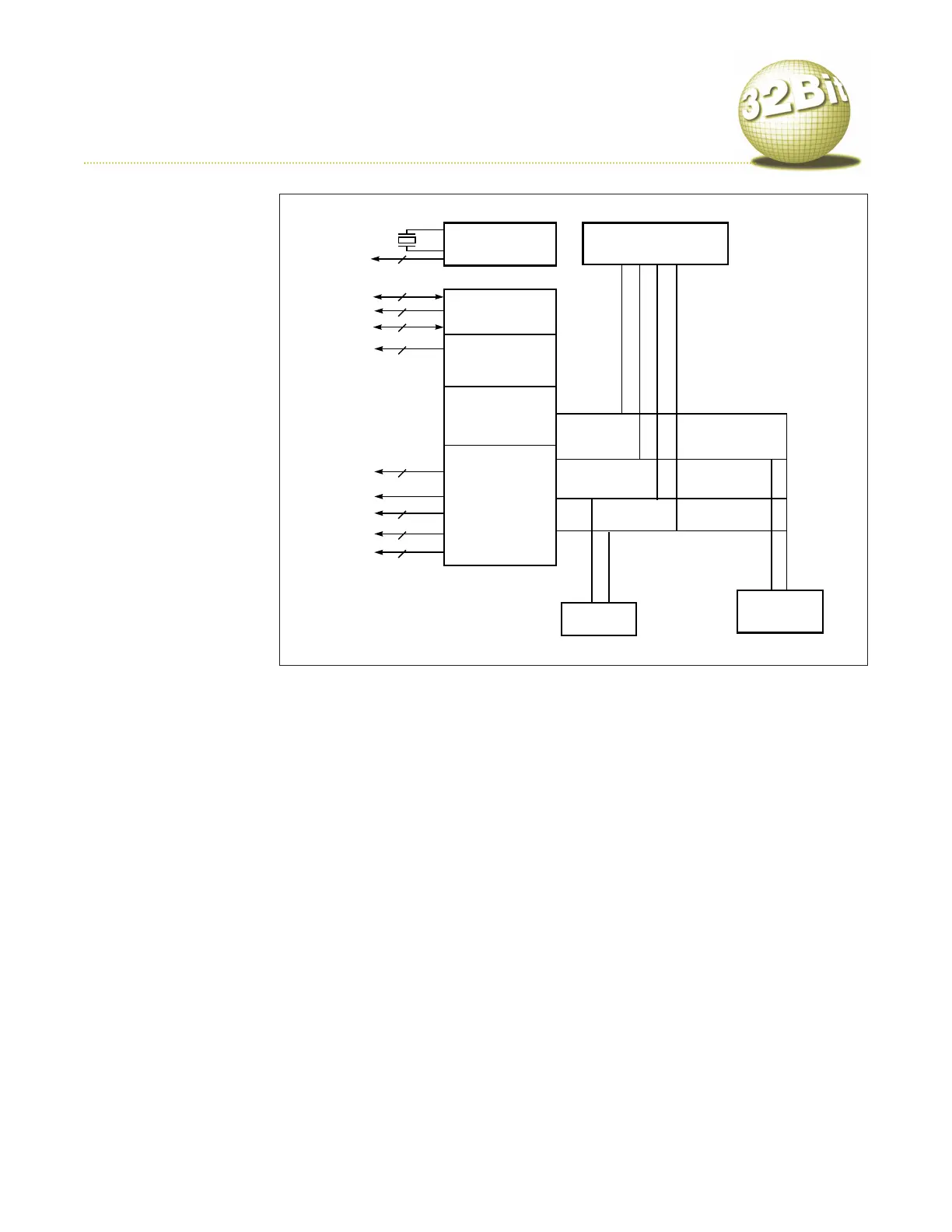

All SPARClite mPs have separate data and instruction

caches. The caches are two-way set-associative and have 16-

or 32-byte cache lines. You can lock and not swap out criti-

cal cache lines on chip. The MB86832 also incorporates a

debug-support unit and an emulator bus, which makes

instruction streams visible even in on-chip cache. Debugging

registers hold data values or addresses for individual and

range breakpoints.

The SPARClite processors run with DRAM, synchronous

DRAM, SRAM, and ROM/EPROM. The memor

y interface

handles page-mode DRAM for low-cost, high-speed access

using a 32-byte burst mode. The memor

y interface includes

a refresh generator for DRAMs, programmable wait states for

slower memory

, and programmable chip selects for memor

y

banking. Boot-up memor

y interfaces are programmable;

SP

ARClite CPUs can boot from 8-, 16-, or 32-bit ROM/

EPROM.

Power management: SP

ARClite processors incorporate

power-down modes, and a power-management register con

-

trols shutdown of the floating-point unit.

Special instr

uctions:

The SP

ARClite implements the SPARC

V8 specification, which includes a hardware multiply instruc

-

tion and a software division using divide by 4. Other special

instructions include scan word looking for first changed bit

or first one or zero, load/store double word, save/restore caller

(uses register windows), tagged add/subtract (generates over

-

flow if most significant bits 0 and 1 are not 0), atomic math

and swap, and generate trap from conditions.

Special on-chip peripherals: SPARClite processors come

with a 24-bit timer that has an 8-bit prescaler and a 16-bit

counter. You can program this counter to operate in period-

ic-interrupt, time-out-interrupt, or square-wave-generator

mode. The mP’s debug-and-support unit (DSU) comprises two

4-bit emulator buses for data and status and two control sig-

nals that enable and set the breakpoint of an in-circuit emu-

lator for hardware debugging and software development. The

SPARClite’s DSU has six breakpoint-descriptor registers and

supports five hardware-monitoring debugging modes.

Development tools: SP

ARClite shares many of the develop-

ment tools that support the SPARC ar

chitecture, including

compilers and debuggers. Fujitsu supplies $89 evaluation kits

and full-featured evaluation boards and monitors. Fujitsu

works with Wind River Systems (www

.windriver

.com), Cho-

rus Systems (www

.sun.com), Accelerated Technology

(www

.atinucleus.com), Microtec (www.microtec.com), JMI

(www.jmi.com), Integrated Systems (www

.isi.com), and L

ynx

(www

.lynx.com) for RTOS support. These vendors also sup-

ply system calls and librar

y routines, many device drivers,

and network protocols. Cygnus (www

.cygnus.com), Wind

River

, and Green Hills Software (www.ghs.com) development

environments also support SP

ARClite. Orion Instruments

(www

.yokogawa.com) in-circuit emulators support SP

ARC-

lite-based system development. US Software (www

.

ussw

.com) and Log Point (www.logpoint.com) offer floating-

point libraries for SP

ARClite.

Second sources: There are no second sour

ces for SPARClite.

Fujitsu SPARClite

Loading...

Loading...