166 b EDN S

EPTEMBER 24, 1998

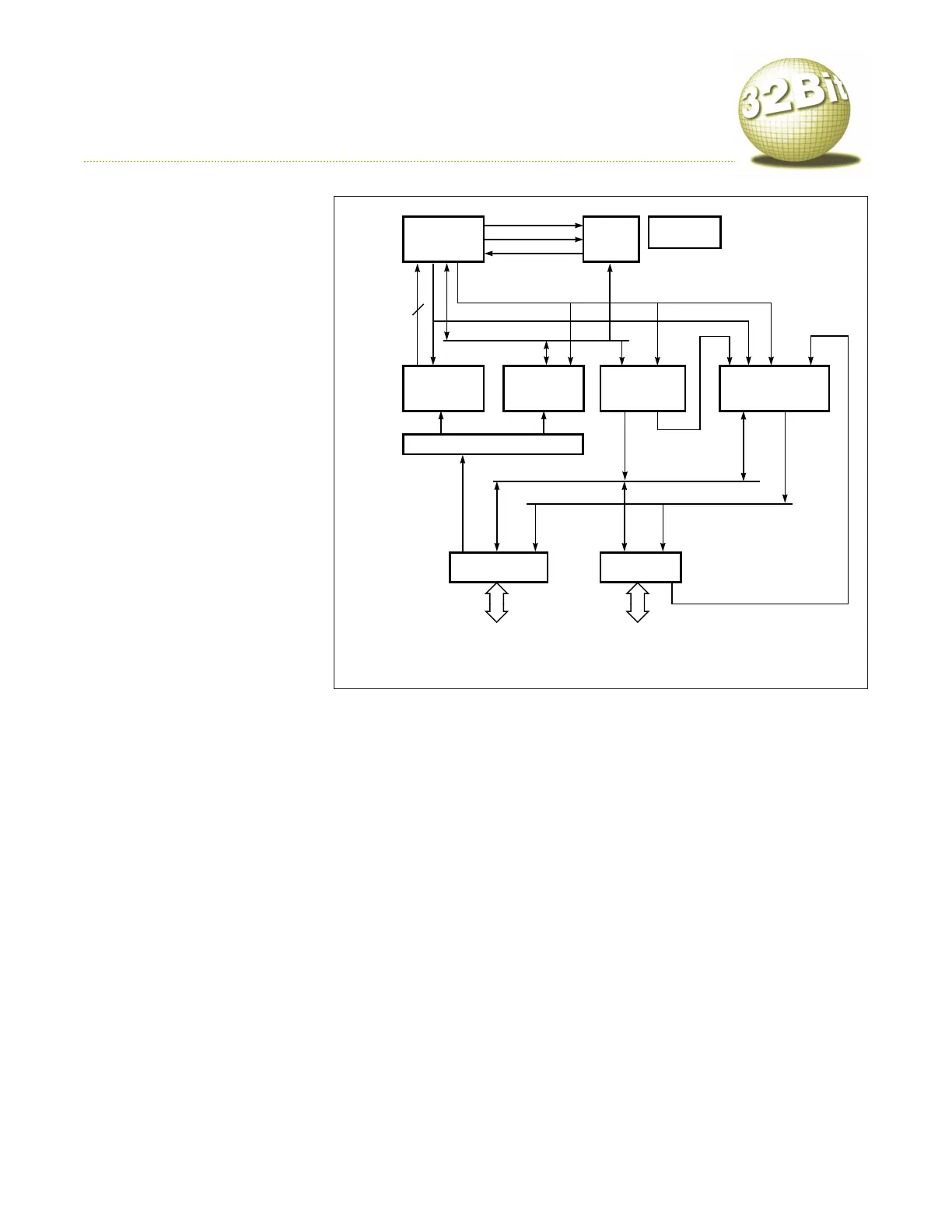

Sun built the microSPARC processors

around a large, multiported register

file that divides into a small set of

global registers for holding global

variables and sets of overlapping reg-

ister windows. Each 24-register win-

dow has a core of eight registers;

eight registers overlapping the previ-

ous and next register windows sup-

plement the eight-register core. The

overlapping registers eliminate the

need to save and restore registers on

function calls, returns, or context

switches between tasks.

The microSPARC has a five-stage

pipeline: fetch, decode, memory

access, execute, and write back. It

also has a four-entry write buffer to

prevent write stalls. A floating-point

unit (FPU) contains 32332-bit float-

ing-point registers, a general-pur-

pose execution unit, and a floating-

point multiplier. A three-entry queue

of floating-point instructions

increases concurrency with integer

execution.

MicroSPARC includes a SPARC-

compliant memory-management

unit (MMU). This MMU uses 3 high-

order bits of physical address to map

eight address spaces. The MMU con-

trols arbitration among I/O, data

cache, instruction cache, and trans-

lation-look-aside-buffer (TLB) references to memory. The

MMU contains a 64-entry, fully associative TLB and supports

256 contexts. The hyperSPARC’s MMU uses a context regis-

ter to identify as many as 4096 contexts.

The microSPARC mPs have a separate 64-bit memory inter-

face that handles as much as 256 Mbytes of 16-Mbit DRAM.

An on-chip, 25-MHz, 32-bit, synchronous Sbus (slave-bus)

interface and controller handle five Sbus slots.

Special instructions: The microSPARC mPs comply with

instructions in the SP

ARC V8 specification. T.sqware’

s

(www.tsqware.com) HDLC controllers include a microSP

ARC

core with built-in DSP capabilities via an extension to the

SP

ARC instruction set and access to hardware operators using

the coprocessor operating code.

Special peripherals: The microSP

ARC-II has an on-chip Sbus

interface. Sun provides peripheral ASICs that attach to the

Sbus and provide memory and I/O capabilities, such as Eth

-

ernet, serial, keyboard, mouse, SCSI, and parallel ports. One

such ASIC, the PCIO chip, links the processor and 10/100-

Mbit Ethernet; an 8-bit expansion bus links to standard

“super-I/O”-like ASICs for connection to keyboards, mice,

serial ports, and the like. The microSP

ARC-IIep contains a PCI

interface for using industr

y-standard peripherals.

Development tools: A variety of OSs, each with its own set

of development tools, supports the microSP

ARC-IIep. Sun’s

Solaris OS features the W

orkshop suite of development tools.

W

orkshop contains a C/C++ compiler and source-code-con

-

trol, debugging, and profiling tools. W

orkshop provides a

self-hosted development environment allowing program-

mers to develop software for embedded applications on their

desktop development workstations. Wind River’s (www.

windriver.com) Tornado provides an integrated suite of

development tools for a cross-platform, host-target environ-

ment. Tornado features graphical host-based tools, a high-

performance RTOS, and host-target communication proto-

cols. Sun’s Chorus group (www.sun.com) features the ClassiX

RTOS. You can compile application code on a Solaris host

with the W

orkshop compiler and debug the code with a Gnu-

based source-level debugger

.

ClassiX also features a Common Object Request Broker

Ar

chitecture (CORBA)-compliant Object Request Broker and

an Interface Definition Language (IDL) compiler. IDL

describes the interface to a routine or function. For example,

IDL defines objects in the CORBA distributed-object envi

-

ronment, which describes the services that the object per

-

forms and how data passes to the object. IDL stores the defi

-

nitions in an interface repositor

y that a client application can

quer

y to determine which functions, or objects, are available

on the object bus. For developers using alternative system

software, the Cygnus (www

.cygnus.com) GnuPro C/C++ tool

kit provides compiling and debugging tools.

Second sources:There are no second sour

ces for microSPARC

devices; however

, Sun licenses the microSPARC core to C-

Cube Microsystems (www

.c-cube.com), Hyundai (www.

hei.co.kr/), Scientific Atlanta (www

.scientific-atlanta.com/),

T

.sqware, and Xylan (www.xylan.com).

Sun microSPARC

Loading...

Loading...