3/24/97 4-17 CPU Organization

of the 64 bytes on the stack is available for handler processing, which should carefully limit

further use of the stack.

Stack Underflow

Stack underflow occurs when too many items are popped and the stack pointer value becomes

greater than its initial value, i.e., the stack top. The XA does not support stack underflow

detection.

Stack Pointer Misalignment

Pointer misalignment occurs when a pointer contains an odd value and is used by an instruction

to access a word value in memory. The same situation could occur if some program action forced

the stack pointer to an odd value. In these cases, the XA ignores the bottom bit of the pointer and

continues with a word memory access.

4.7.5 Stack Initialization

At power-on reset, both USP and SSP in all XA derivatives are initialized to 100h. Since SP is

pre-decremented, the first PUSH operation will store a word at location FEh and the stack will

grow downwards from there.

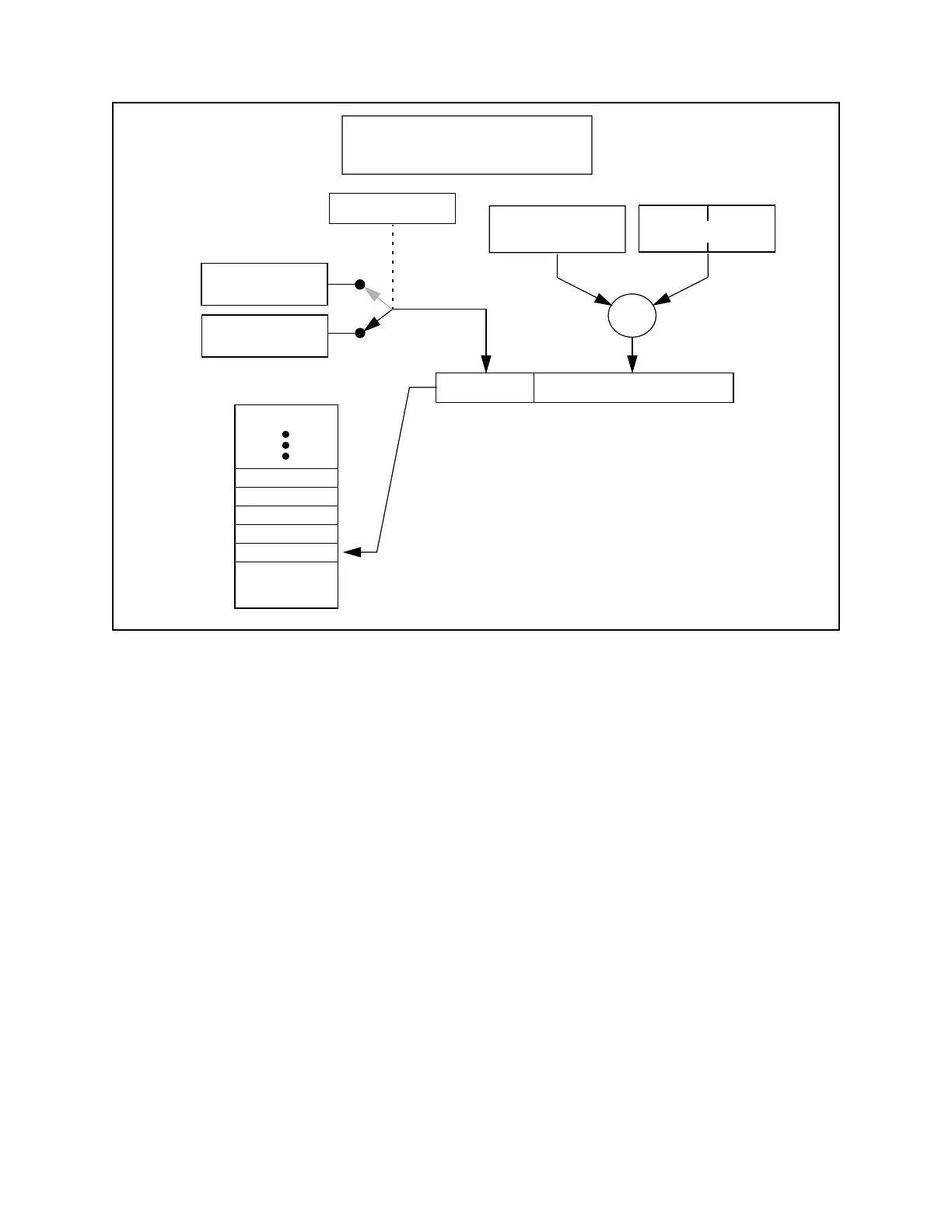

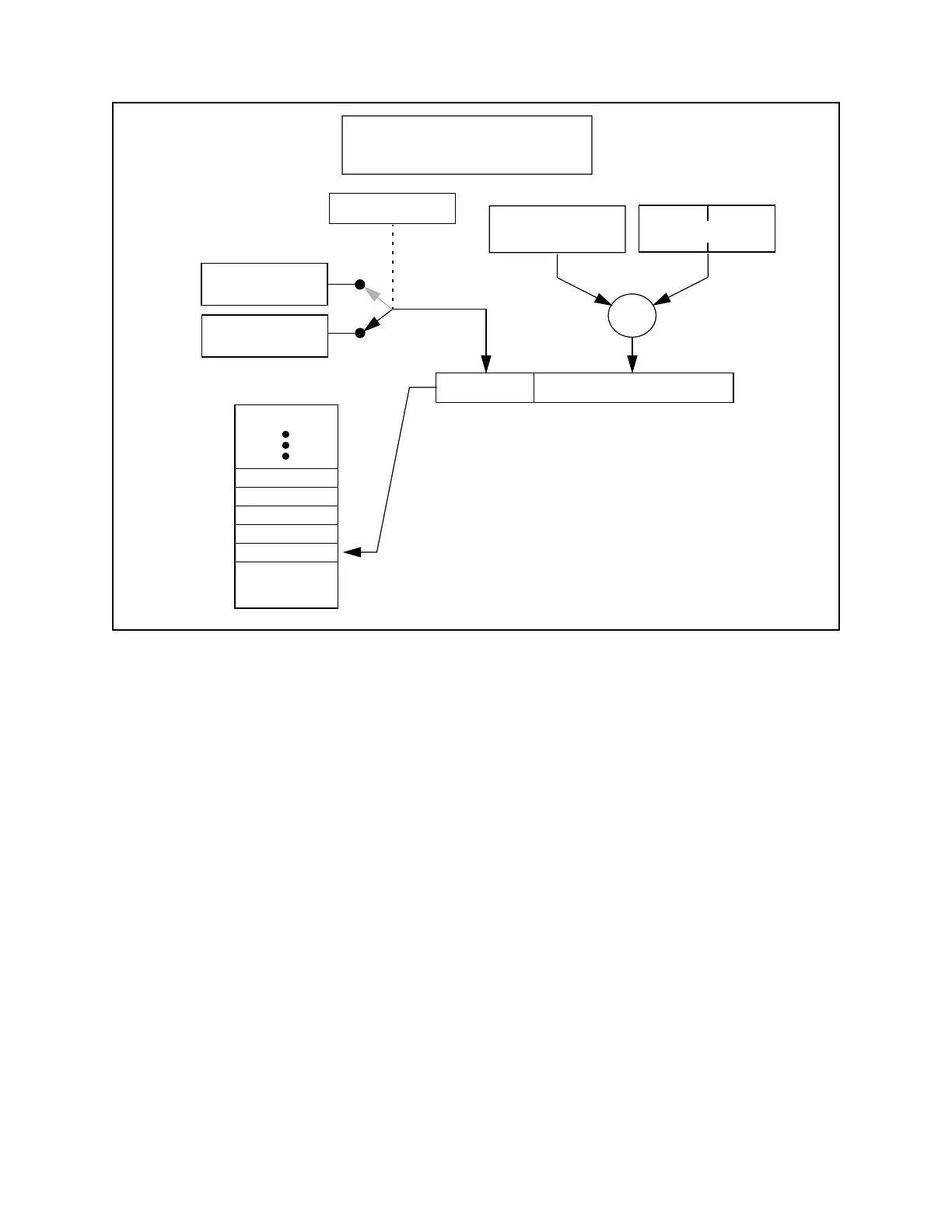

Figure 4.14 Stack-based addressing

MOV Rn, [R7+offset]

MOV [R7+offset], Rn

DS

SP (R7)

8-bit segment

identifier

16-bit pointer

0

1

SM bit in PSW

complete 24-bit

memory address

00h

[SP+2]

[SP+4]

[SP+6]

[SP+8]

[SP+0]

Data Memory

8 or 16-bit offset

(from instruction)

+

16 bits

8 bits

Loading...

Loading...