XA User Guide 6-40 4/17/98

ADDC [Rd+offset16], Rs

Bytes: 4

Clocks: 6

Operation: ((WS:Rd)+offset16) <-- ((WS:Rd)+offset16) + (Rs) + (C)

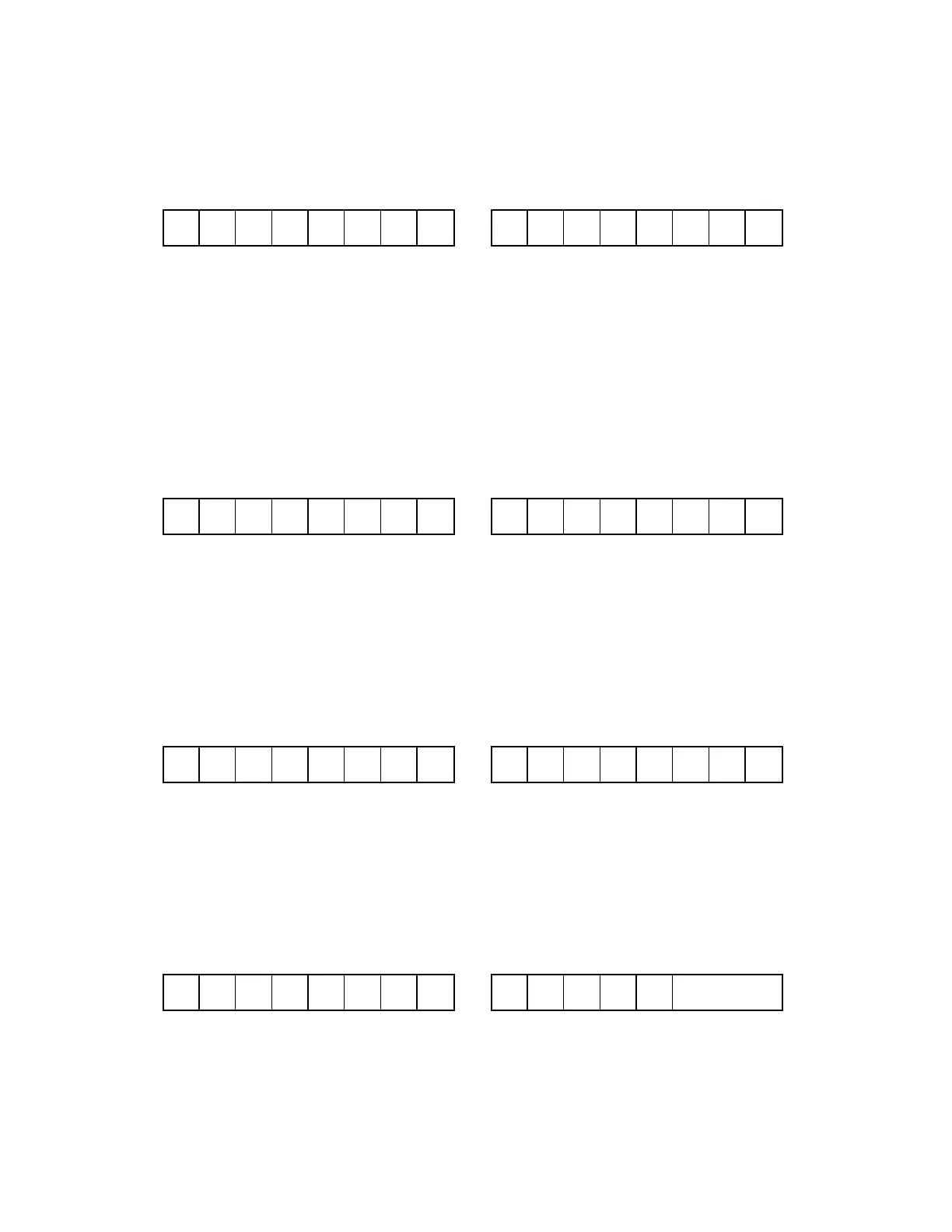

Encoding:

byte 3: upper 8 bits of offset16

byte 4: lower 8 bits of offset16

ADDC Rd, [Rs+]

Bytes: 2

Clocks: 5

Operation: (Rd) <-- (Rd) + ((WS:Rs)) + (C)

(Rs) <-- (Rs) + 1 (byte operation) or 2 (word operation)

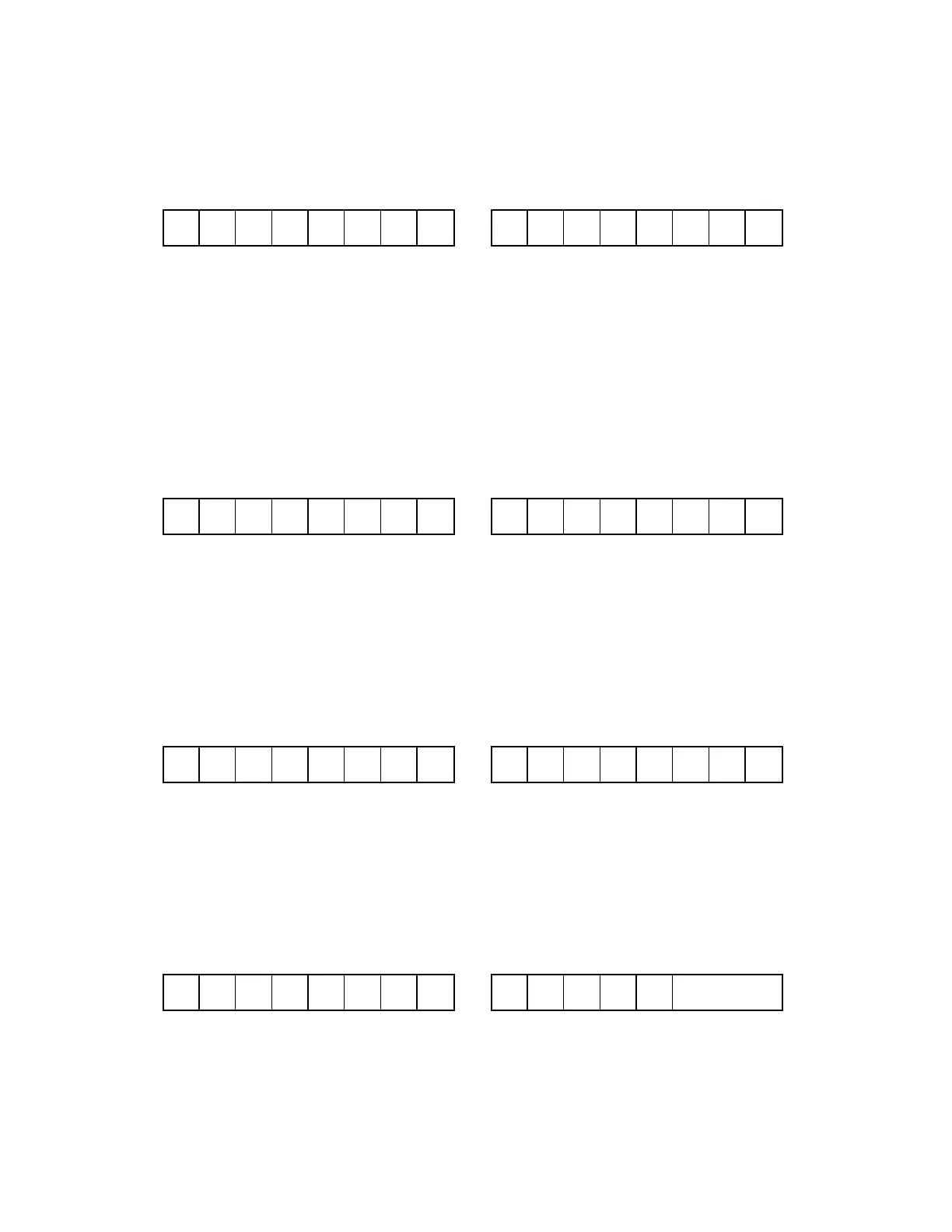

Encoding:

ADDC [Rd+], Rs

Bytes: 2

Clocks: 5

Operation: ((WS:Rd)) <-- ((WS:Rd)) + (Rs) + (C)

(Rd) <-- (Rd) + 1 (byte operation) or 2 (word operation)

Encoding:

ADDC direct, Rs

Bytes: 3

Clocks: 4

Operation: (direct) <-- (direct) + (Rs) + (C)

Encoding:

byte 3: lower 8 bits of direct

0 0 0 1 SZ 1 0 1 s s s s 1 d d d

0 0 0 1 SZ 0 1 1 d d d d 0 s s s

0 0 0 1 SZ 0 1 1 s s s s 1 d d d

0 0 0 1 SZ 1 1 0 s s s s 1 direct: 3 bits

Loading...

Loading...