XA User Guide 6-58 4/17/98

ASR Rd, Rs

Bytes: 2

Clocks: For 8/16 bit shifts -> 4 + 1 for each 2 bits of shift

For 32 bit shifts -> 6 + 1 for each 2 bits of shift

Operation:

Encoding:

ASR Rd, #data4

Rd,#data5

Operation:

Bytes: 2

Clocks: For 8/16 bit shifts -> 4 + 1 for each 2 bits of shift

For 32 bit shifts -> 6 + 1 for each 2 bits of shift

Encoding: (for byte and word data sizes)

(for double word data size)

Note: SZ1/SZ0 = 00: byte operation; SZ1/SZ0 = 10: word operation; SZ1/SZ0 = 11: double word

operation.

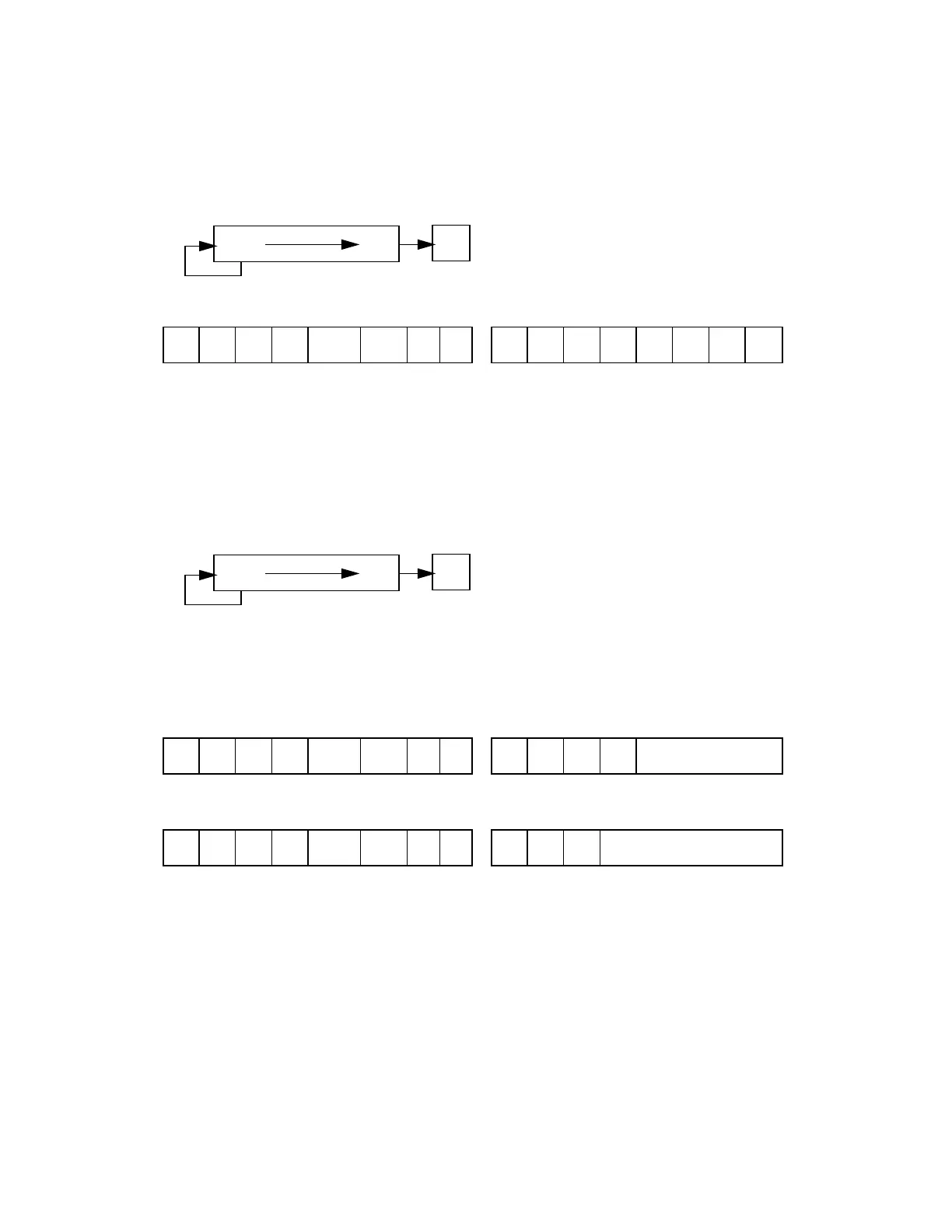

CMSB LSB

(Rd)

d d d d s s s s1 1 0 0 SZ1 SZ0 1 0

CMSB LSB

(Rd)

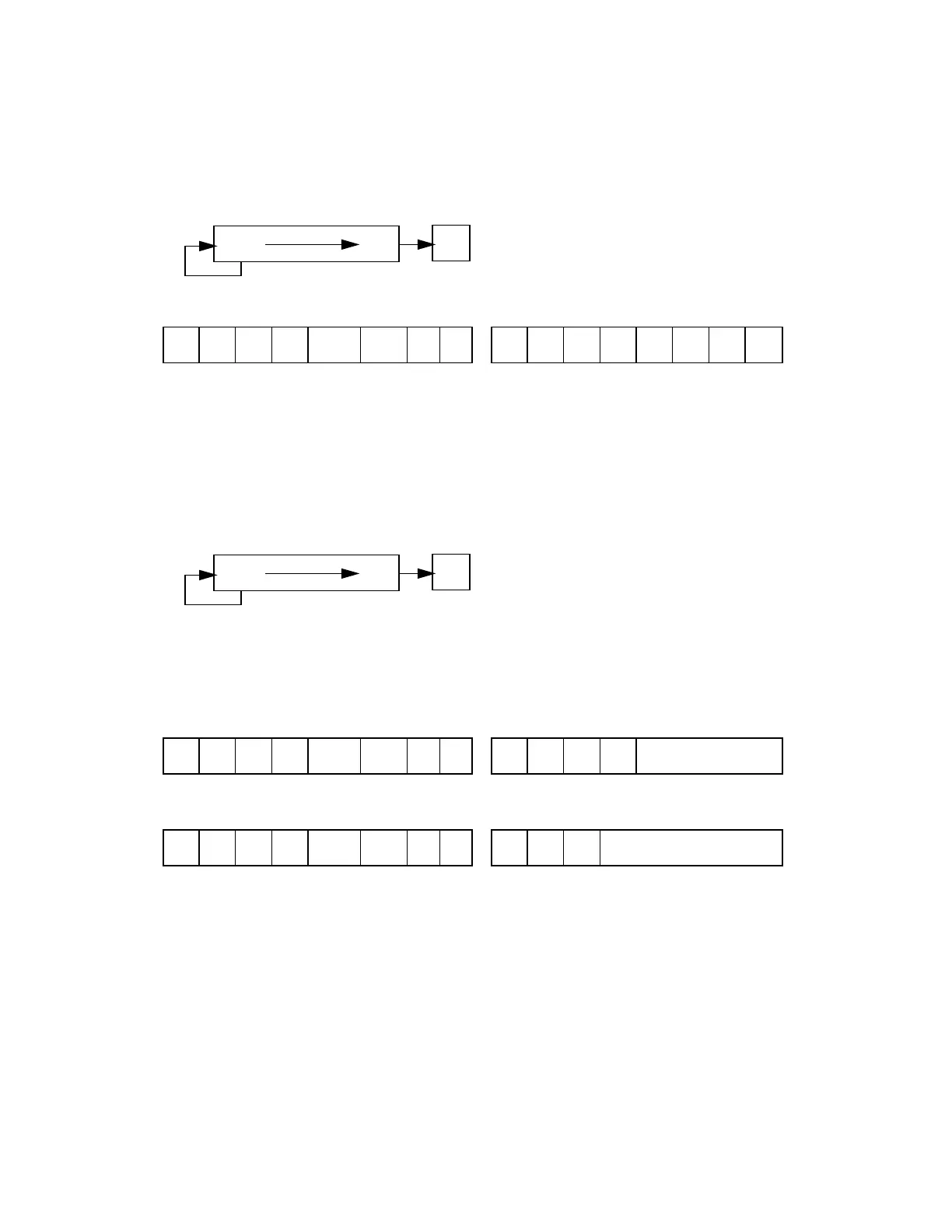

d d d d #data41 1 0 1 SZ1 SZ0 1 0

d d d #data51 1 0 1 SZ1 SZ0 1 0

Loading...

Loading...