4/17/98 6-101 Addressing Modes and Data Types

JMP Jump Indirect through Register

Syntax: JMP [Rs]

Operation: (PC) <-- (PC) + 2

(PC.15-1) <-- (Rs.15-1) (note that PC.

23-16 is not affected)

(PC.0) <-- 0

Description: Causes an unconditional branch to the address contained in the operand word

register, anywhere within the 64K code page following the JMP instruction.The value of the PC

used in the target address calculation is the address of the instruction following the JMP

instruction.

The target address must be word aligned as JMP will force PC.bit0 to 0.

Size: none

Flags Updated: none

Bytes: 2

Clocks: 7

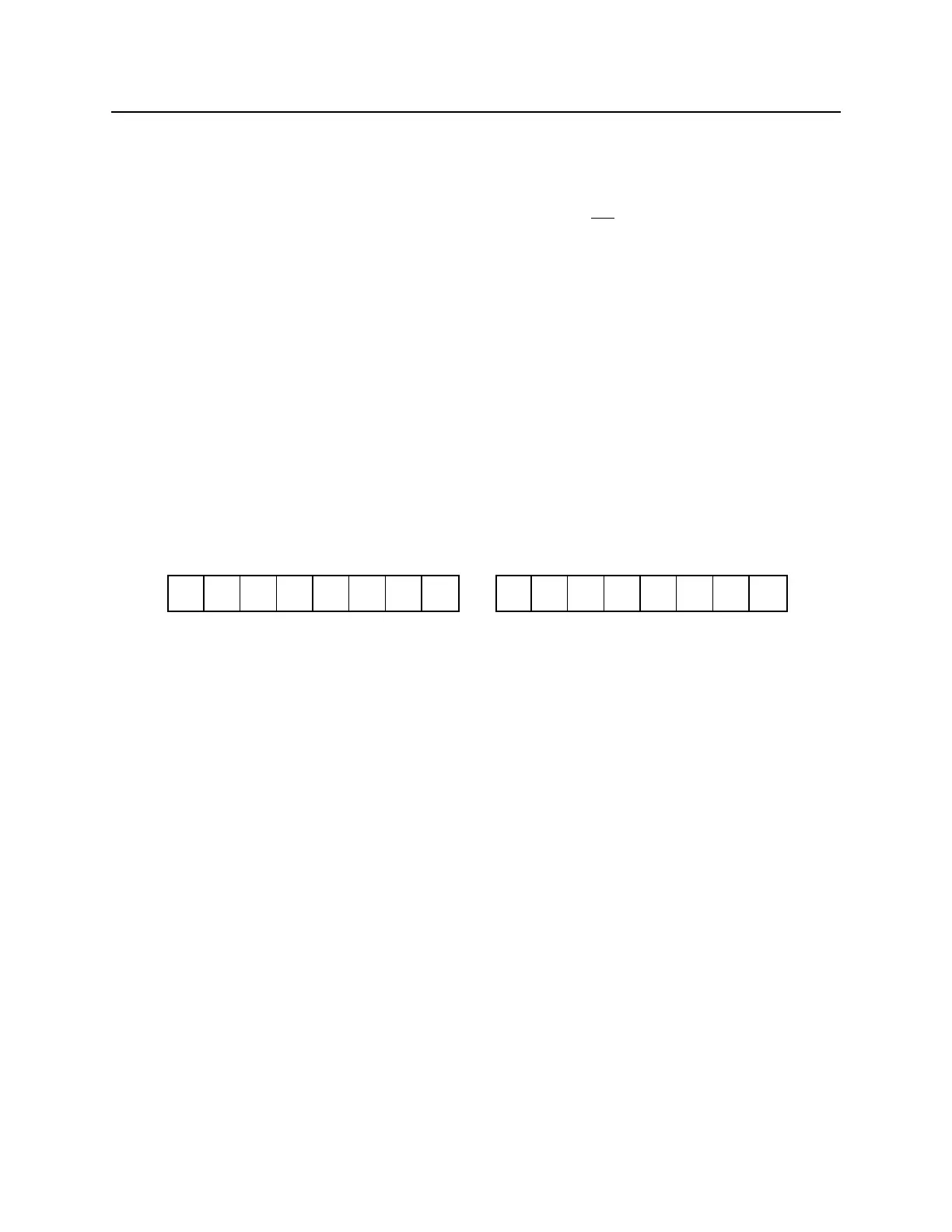

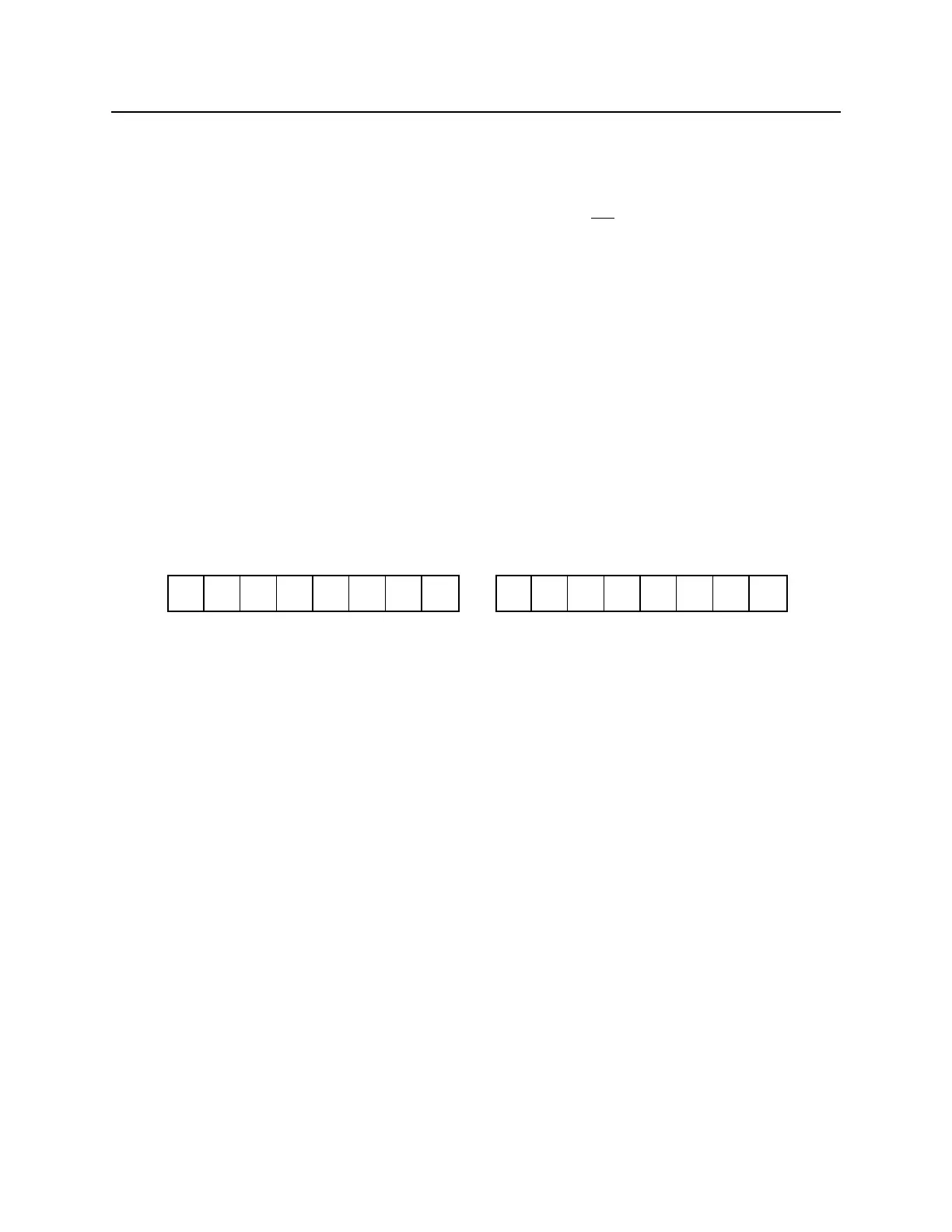

Encoding:

1 1 0 1 0 1 1 0

0 1 1 1 0 s s s

Loading...

Loading...