XA User Guide 6-102 4/17/98

JMP Jump indirect through register

Syntax: JMP [A+DPTR]

Operation: (PC) <-- (PC) + 2

(PC15-1) <-- (A) + (DPTR)

(PC.0) <-- 0

Description: Causes an unconditional branch to the address formed by the sum of the 80C51

compatibility registers A and DPTR, anywhere within the 64K code page following the JMP

instruction. This instruction is included for 80C51 compatibility. See Chapter 9 for details of

80C51 compatibility features.

Note: The target address must be word aligned as JMP will force PC.bit0 to 0.

Flags Updated: none

Bytes:2

Clocks:5

Note: A and DPTR are pre-defined registers used for 80C51 code translation.

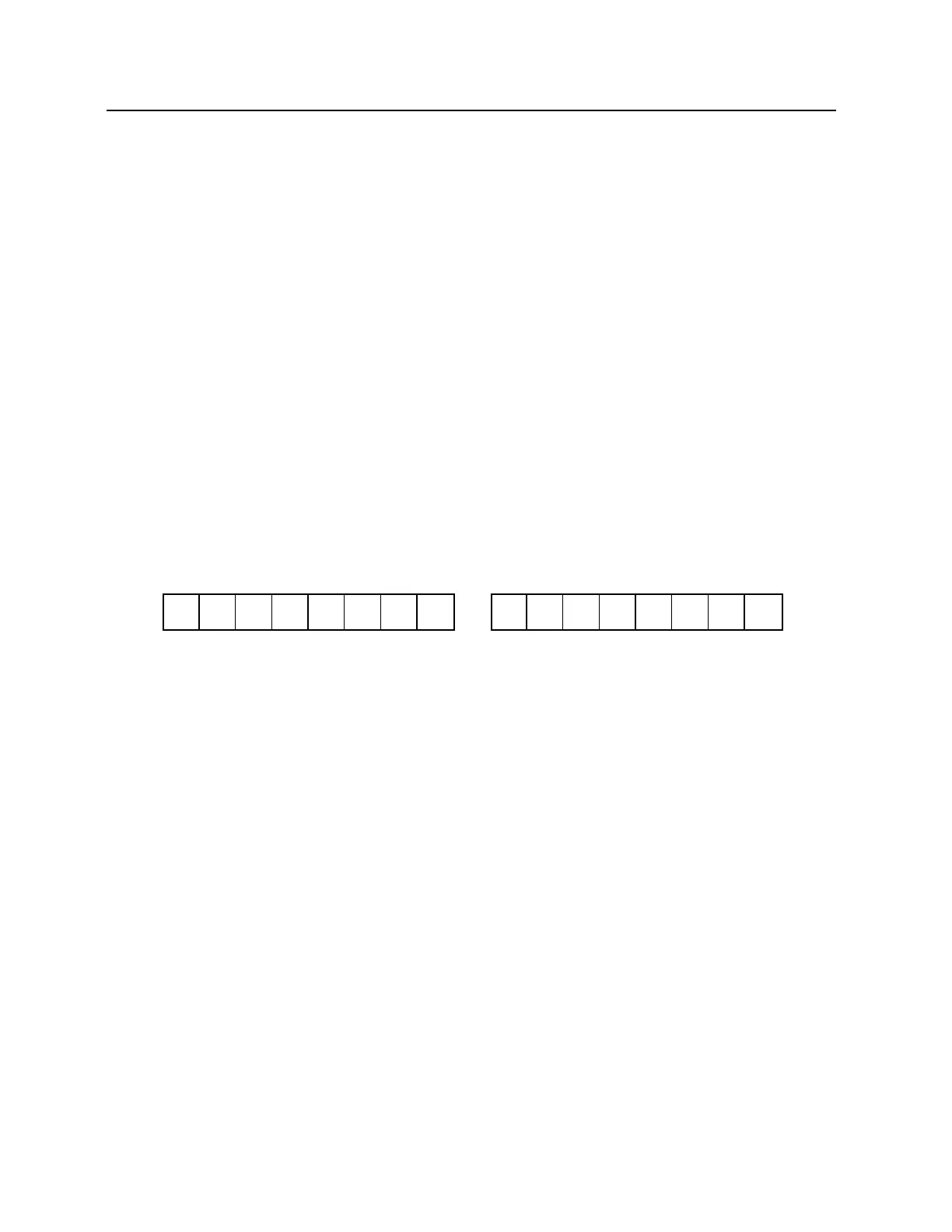

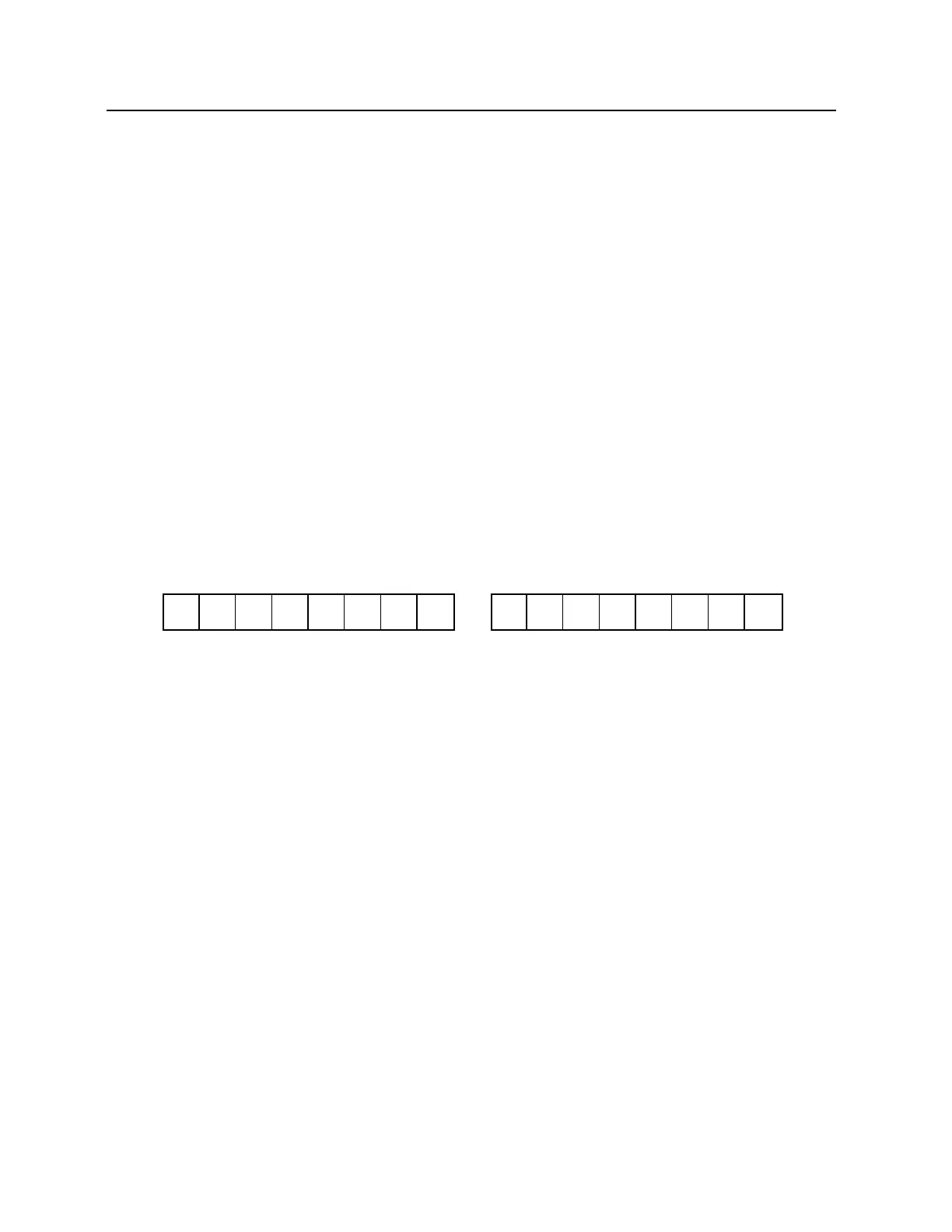

Encoding:

1 1 0 1 0 1 1 0

0 1 0 0 0 1 1 0

Loading...

Loading...