XA User Guide 6-176 4/17/98

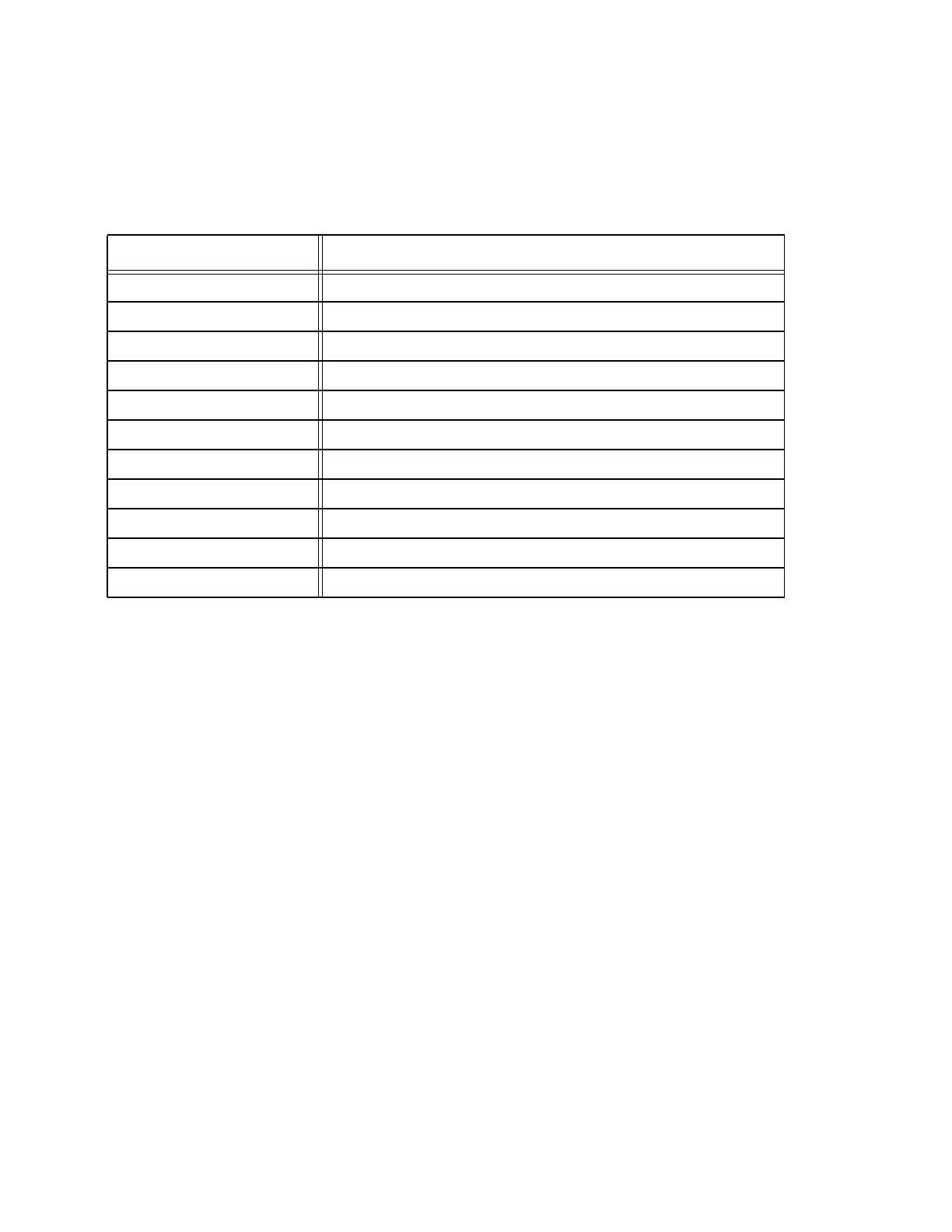

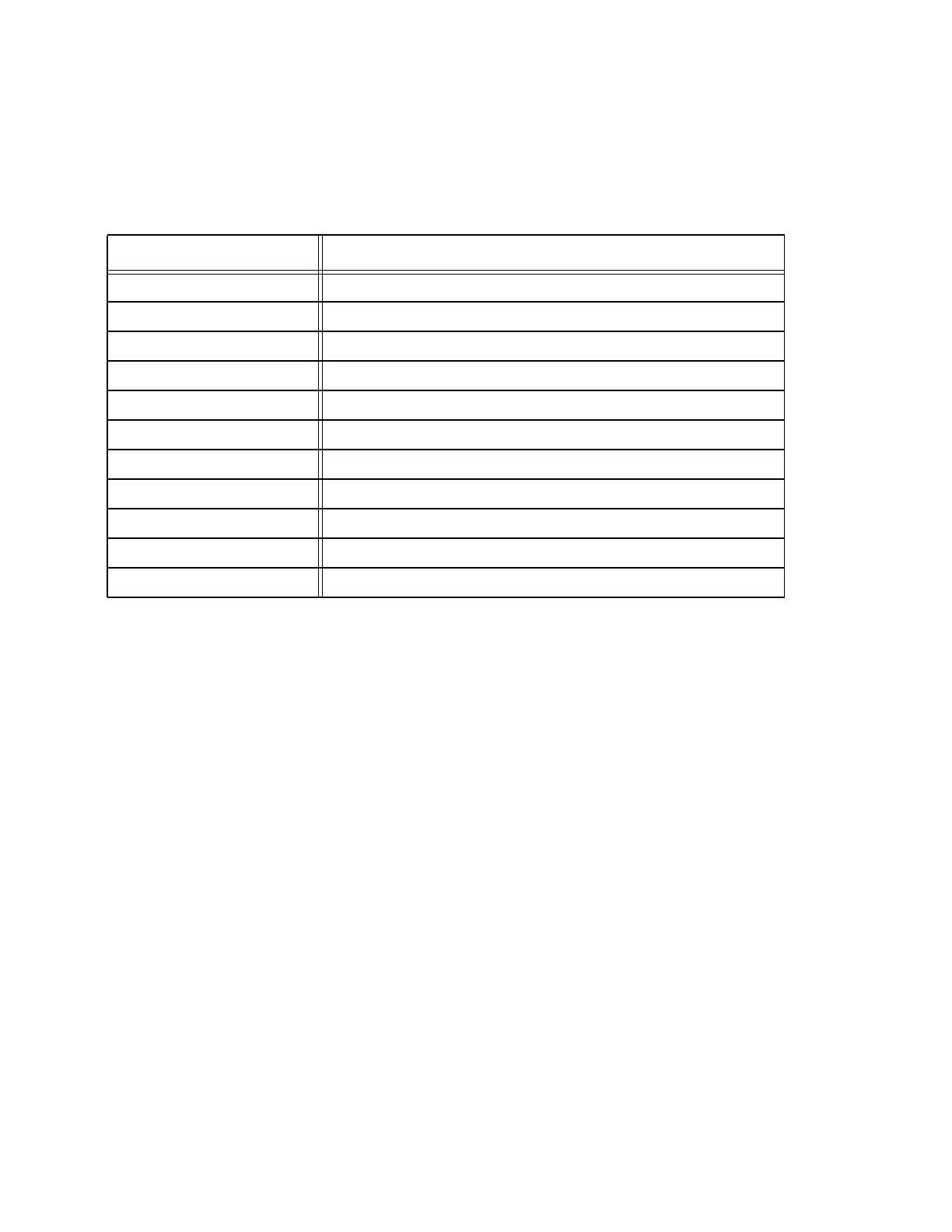

6.6 Summary Of Illegal Operand Combinations On The XA

All but one case are instructions that specify or imply 2 write operations to a single register file

location within a single instruction. The other case is a possible corruption of the source register

data by an auto-increment before it is read. These conditions are not detected by XA hardware. The

instruction/operand combinations indicated should not be used when writing XA code.

NOTES:

1 This addressing mode is illegal when the source and destination are the same register. This would cause

both a data write and an auto-increment operation to the same register.

2 This instruction is illegal when the source and destination pointer registers are the same register. This

would cause two auto-increment operations to the same register.

3 This instruction is illegal when the source and destination are the same register. The source register would

be auto-incremented and read at the same time, with an undefined result.

4 This instruction is illegal when the source and destination are the same register. This would cause two

writes to the same register.

5 This addressing mode is illegal when the indirect address of the destination points to the pointer register

itself in the register file. This is possible only when 8051 compatibility mode is enabled. This would

cause both a data write and an auto-increment operation to the same register.

6 This instruction is illegal when the indirect address of the source operand points to the destination register

itself in the register file. This is possible only when 8051 compatibility mode is enabled. This would

cause two writes to the same register.

7 This instruction is illegal when the direct address of the source operand points to the destination register

itself in the register file. This is possible only when 8051 compatibility mode is enabled. This would

cause two writes to the same register.

8 A POP to R7 (the stack pointer) would cause both a data write and an auto-increment operation to the

same register.

Instruction(s) affected Reason for illegal combination

(any op) Rx, [Rx+] Auto-increment plus explicit write

1

mov [Rx+], [Rx+] Double auto-increment of one register

2

(any op) [Rx+], Rx Auto-increment write may corrupt the source register before it is read

3

NORM Rx, Rx Result and shift count stored in the same register

4

XCH Rx, Rx Double write of a single register

4

(any op) [Rx+], Ry Auto-increment plus indirect write to same register

5

(any op) [Rx+], [Ry+] Auto-increment plus indirect write to same register

5

(any op) [Rx+], #data Auto-increment plus indirect write to same register

5

XCH Rx, [Rx] Indirect write plus explicit write to the same register

6

XCH Rx, direct Direct write plus explicit write to the same register

7

POP R7 Stack pointer auto-increment plus explicit write to R7/SP

8

Loading...

Loading...