XA User Guide 7-4 4/17/98

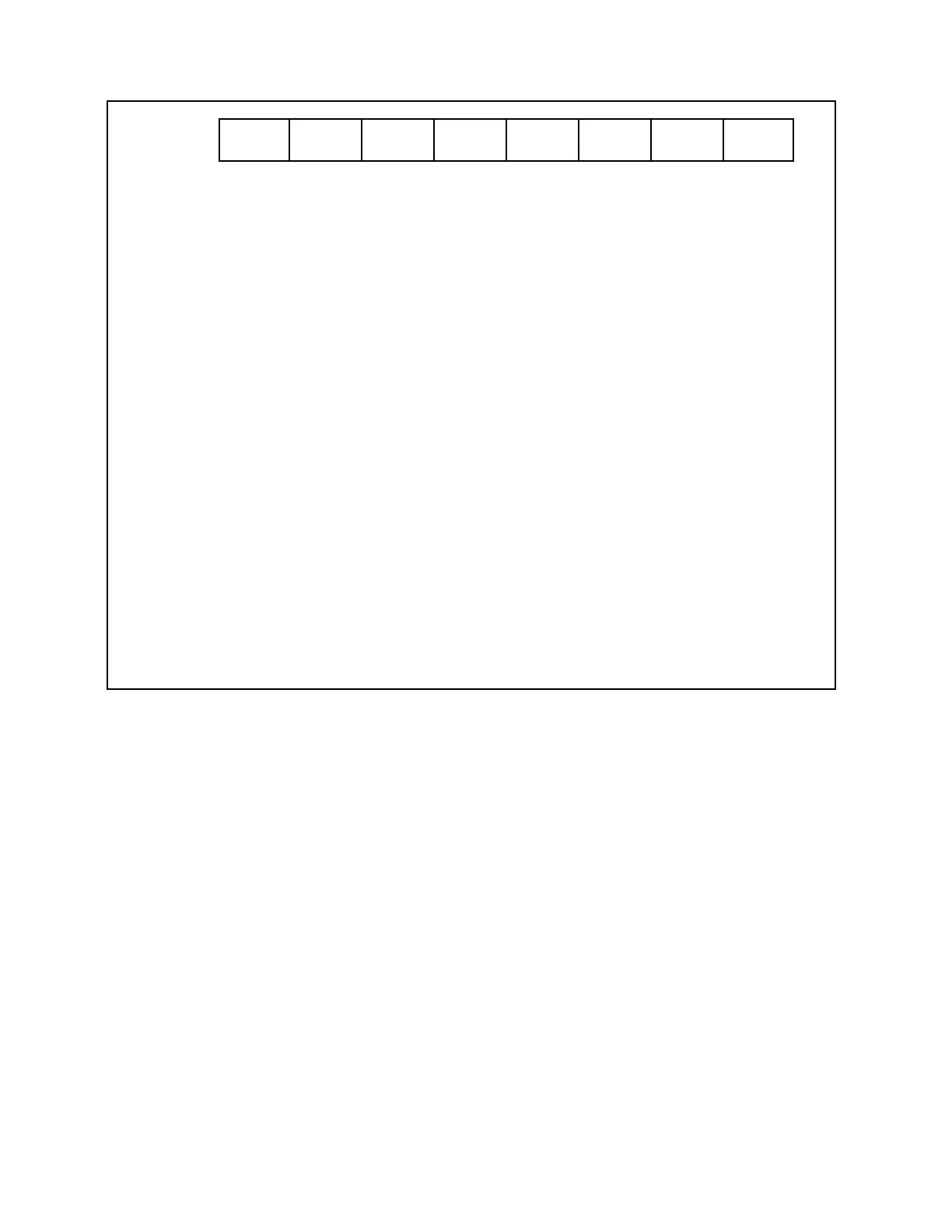

Figure 7.1 Bus Configuration Register (BCR)

- WAITD-- BUSD BC2 BC1 BC0

BCR

WAITD: WAIT disable. Causes the XA external bus interface to ignore the value on the

WAIT input. This allows tying the WAIT input high for applications that use

internal code and do not need the WAIT function.

BUSD: Bus disable. Causes XA external bus functions to be disabled permanently.

The primary purpose of this is to allow prevention of inadvertent activation of

the bus by an instruction pre-fetch when the XA is executing code near the end

of the on-chip code memory.

BC2 - BC0: These bits select the XA external bus configuration, specifically the number of

data bits and the number of address lines. The supported combinations are

shown below.

000 : 8-bit data bus, 12 address lines

001 : 8-bit data bus, 16 address lines

010 : 8-bit data bus, 20 address lines

011 : 8-bit data bus, 24 address lines

100 : < function reserved >

101 : < function reserved >

110 : 16-bit data bus, 20 address lines

111 : 16-bit data bus, 24 address lines

"-" Reserved for possible future use. Programs should take care when writing to

registers with reserved bits that those bits are given the value 0. This will

prevent accidental activation of any function those bits may acquire in future

XA CPU implementations.

Loading...

Loading...