XA User Guide 7-14 4/17/98

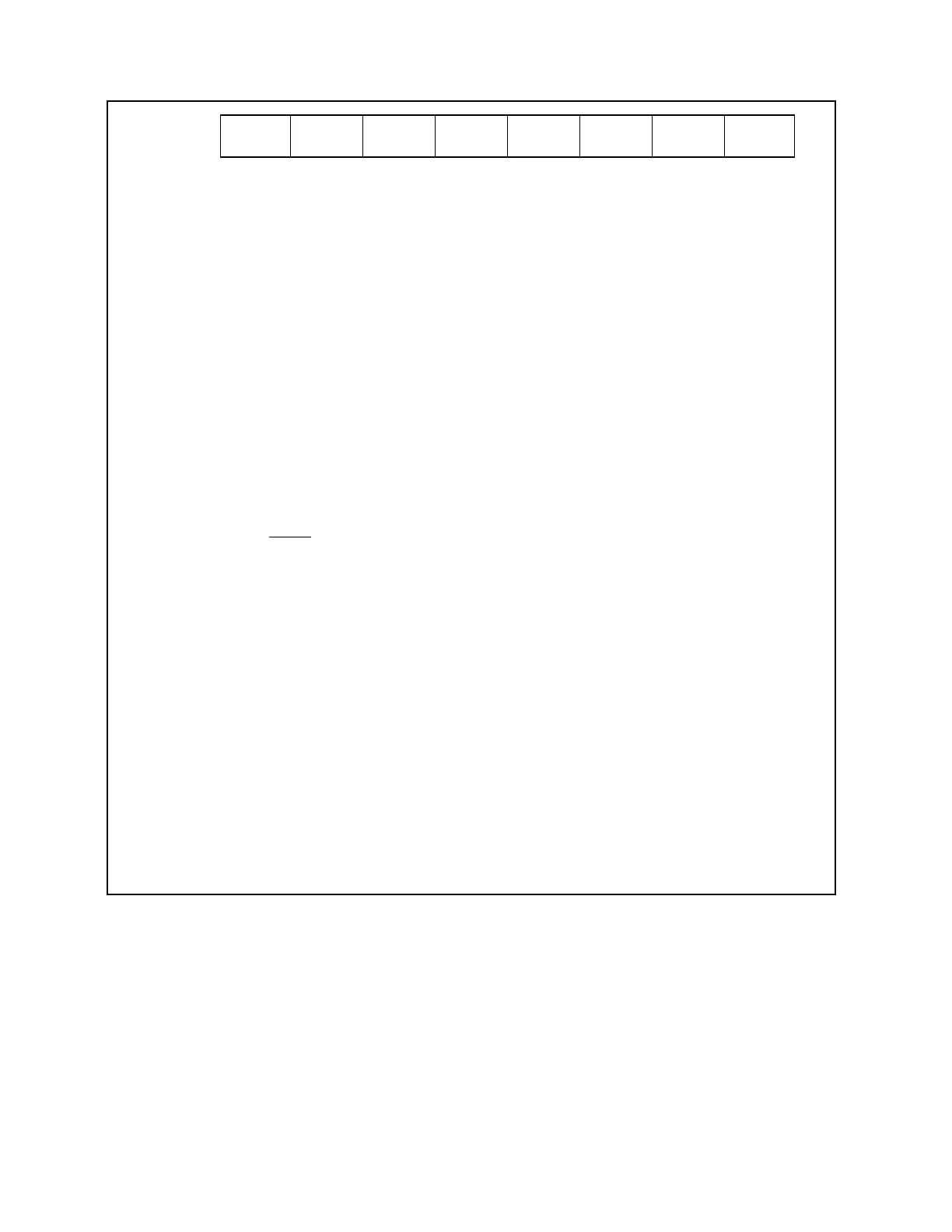

Figure 7.13 Bus Timing Register Low Byte (BTRL)

WM1 WM0 ALEW - CR0CR1 CRA1 CRA0

BTRL

WM1: Write Mode 1. Selects the width of the write pulse.

0 : Write pulse (WR) width is 1 CPU clock.

1 : Write pulse (WR) width is 2 CPU clocks.

WM0: Write Mode 0. Selects the data hold time.

0 : Data hold time is minimum (0 clocks).

1 : Data hold time is 1 CPU clock.

ALEW: ALE width selection. Determines the duration of ALE pulses.

0 : ALE width is one half of one CPU clock.

1 : ALE width is one and a half CPU clocks.

CR1, CR0: Code Read. Selects the length of a code read cycle when ALE is not used.

00 : Code read cycle is 1 clocks in duration.

01 : Code read cycle is 2 clocks in duration.

10 : Code read cycle is 3 clocks in duration.

11 : Code read cycle is 4 clocks in duration.

CRA1, CRA0: Code Read with ALE. Selects the length of a code read cycle when ALE is used prior

to PSEN being asserted.

00 : Code read cycle is 2 clocks in duration.

01 : Code read cycle is 3 clocks in duration.

10 : Code read cycle is 4 clocks in duration.

11 : Code read cycle is 5 clocks in duration.

"-" Reserved for possible future use. Programs should take care when writing to registers

with reserved bits that those bits are given the value 0. This will prevent accidental

activation of any function those bits may acquire in future XA CPU implementations.

Notes:

- See text regarding disallowed bus timing combinations.

- The bit pairs DW1:0, DWA1:0, DR1:0, DRA1:0, CR1:0, and CRA1:0 determine the length of entire

bus cycles of different types. Bus cycles with an ALE begin when ALE is asserted. Bus cycles without

an ALE begin when the bus strobe is asserted or when the address changes (in the case of burst

mode code reads). Bus cycles end either when the bus strobe is de-asserted or when data hold time

is completed (in the case of a data write with extra hold time, see bit WM0).

Loading...

Loading...