XA User Guide 9-2 3/24/97

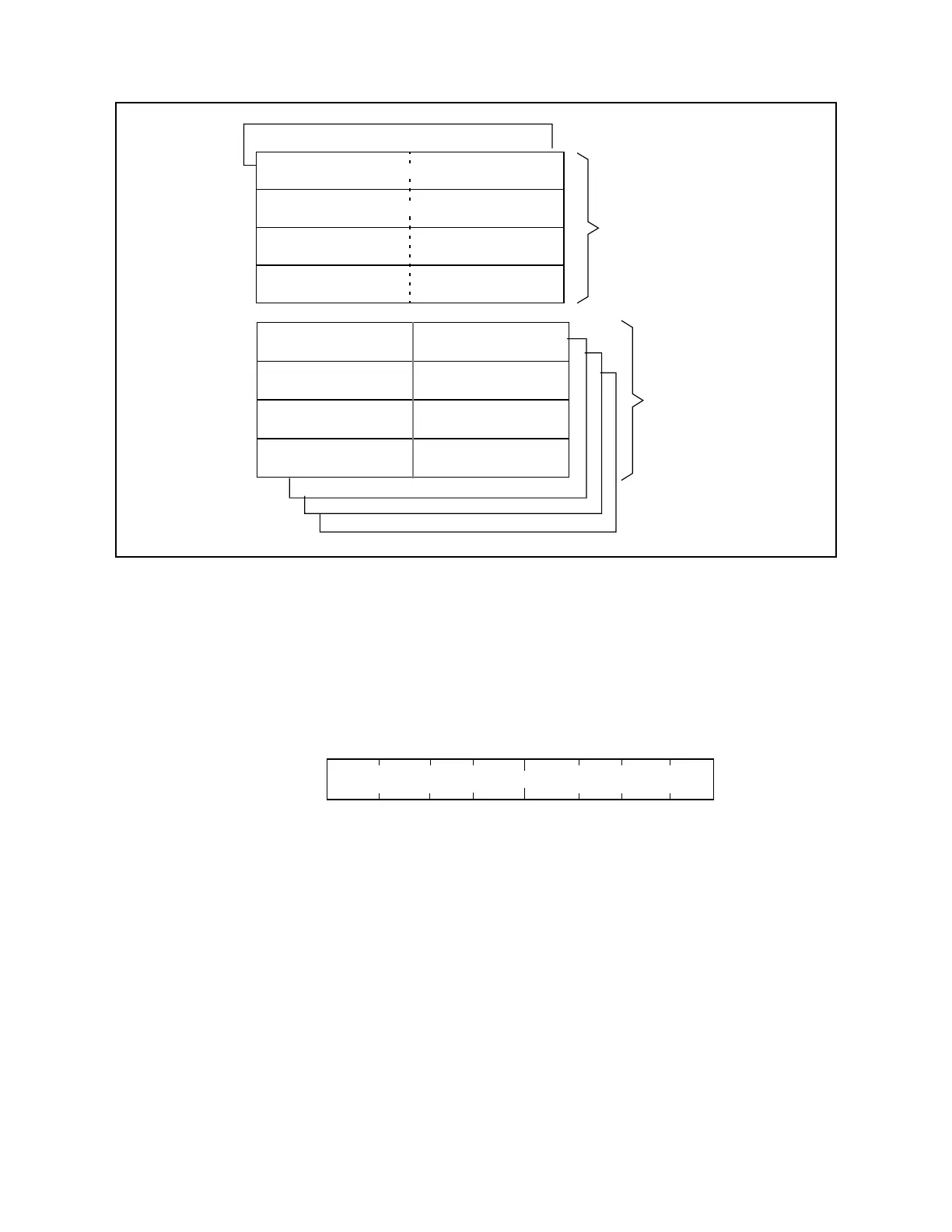

Figure 9.1. XA Register File

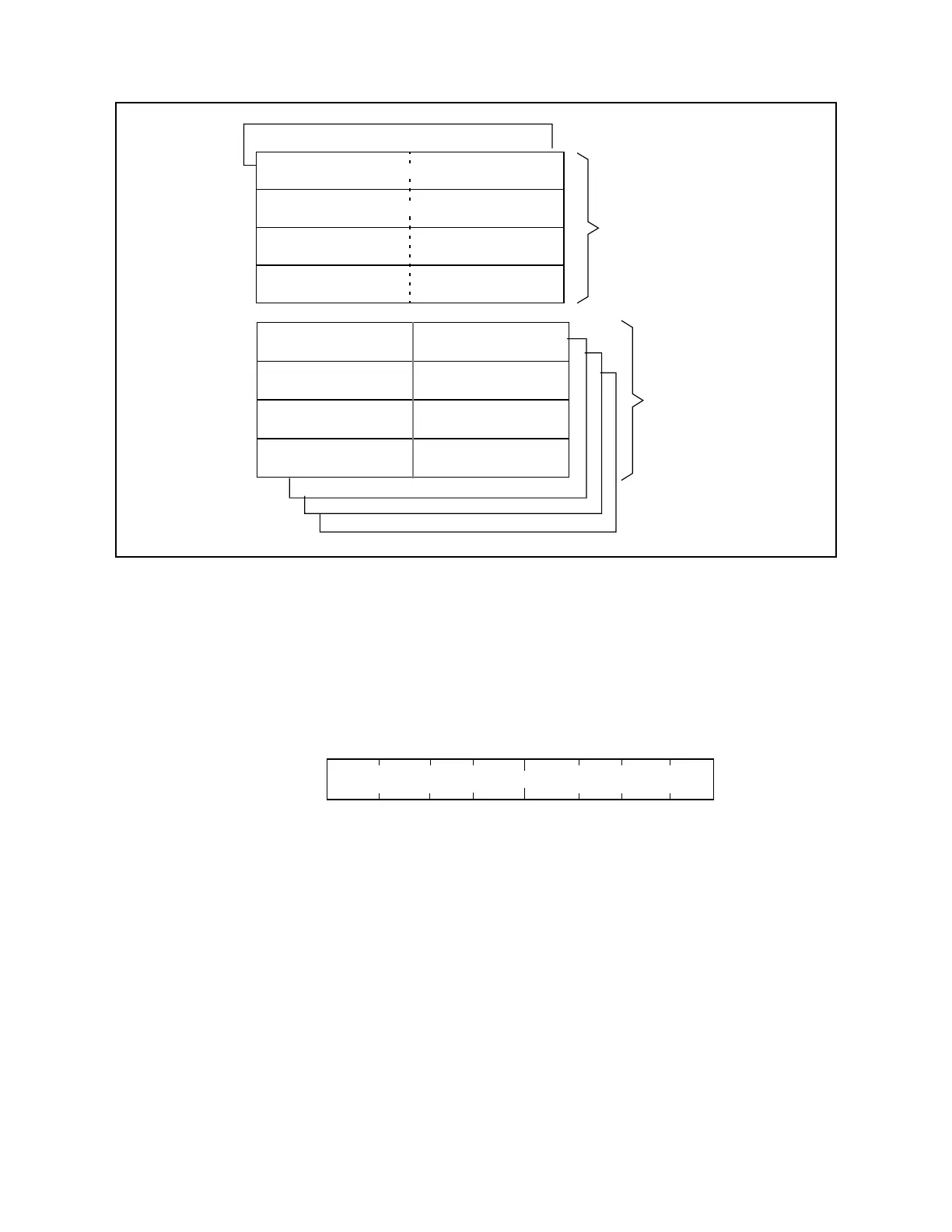

Other important registers of the 80C51 are provided in other ways. The program status word

(PSW) of the XA is slightly different than the 80C51 PSW, so a special SFR address is reserved

to provide an 80C51 compatible "view" of the PSW for use by translated code. This alternate

PSW, called PSW51, is shown in the figure 9.2. The F0 flag and the F1 flag are simply readable

and writable bits. The P flag provides an even parity bit for the 80C51 A register and always

reflects the current contents of that register. Note that the P flag, the F0 flag, and the F1 flag only

appear in the PSW51 register.

The 80C51 indirect data memory access mode, using R0 or R1 as pointers, requires special

support on the XA, where pointers are normally 16 bits in length. The 80C51 compatibility mode

also causes the XA to mimic the 80C51 indirect scheme, using the first two bytes of the register

file as indirect pointers, each zero extended to make a 16-bit address. Due to this and the

previously mentioned register overlap to memory feature, the compatibility mode must be turned

on in order to execute most translated 80C51 code on the XA. Other than the two

aforementioned effects, nothing else about XA functioning is affected by the compatibility mode.

Figure 9.2. PSW CPU status flags

R7

R6

R5

R4

R3

R2

R1

R0

R7H

R6H = DPH

R5H

R4H = B

R3L

R2L

R1L

R0L

R7L

R6L = DPL

R5L

R3H

R2H

R1H

R0H

R4L = A (ACC)

Global registers.

SSP

Banked Registers

USP

DPTR

PSW51

C

AC POV F1 F0

RS1 RS0

Loading...

Loading...