3/24/97 9-13 8051 Compatibility

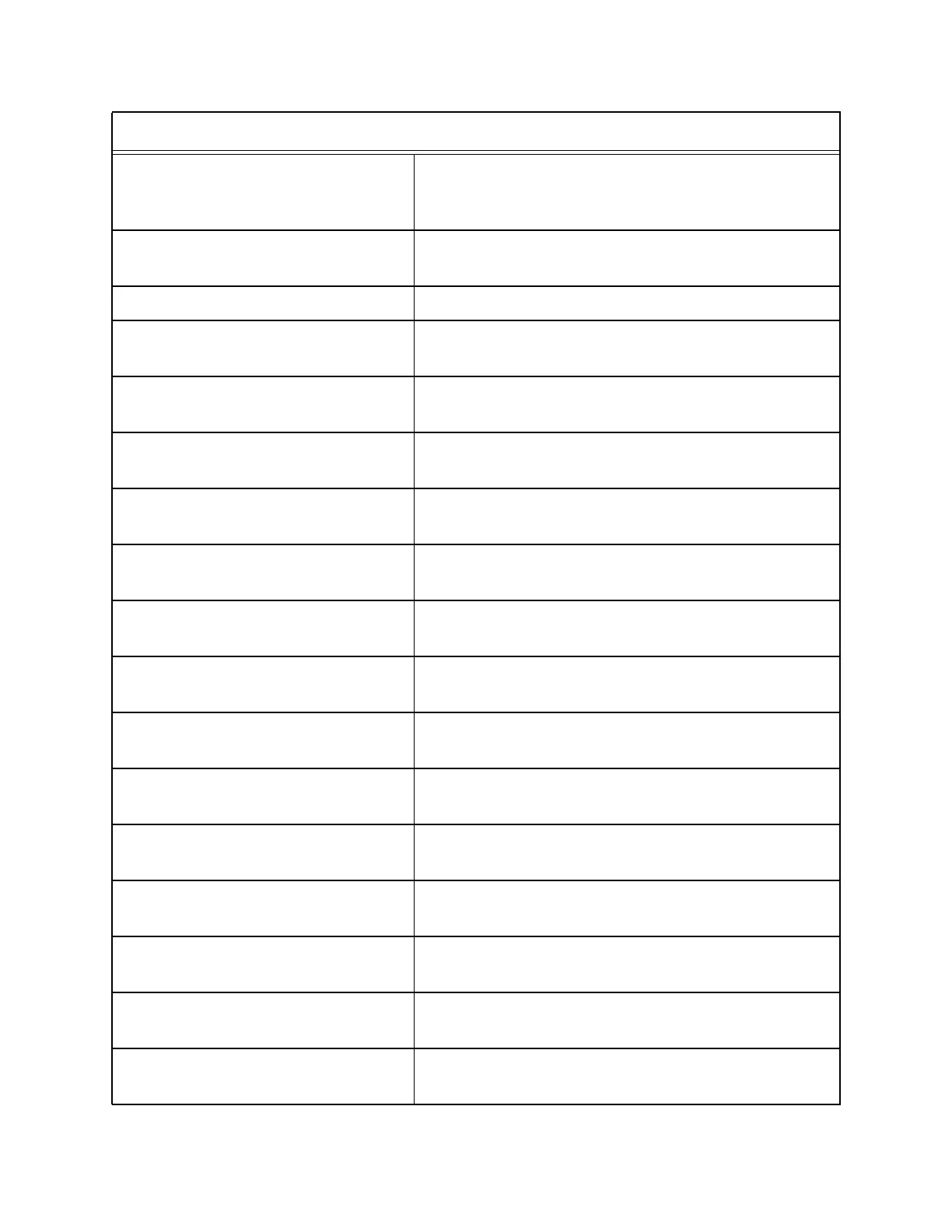

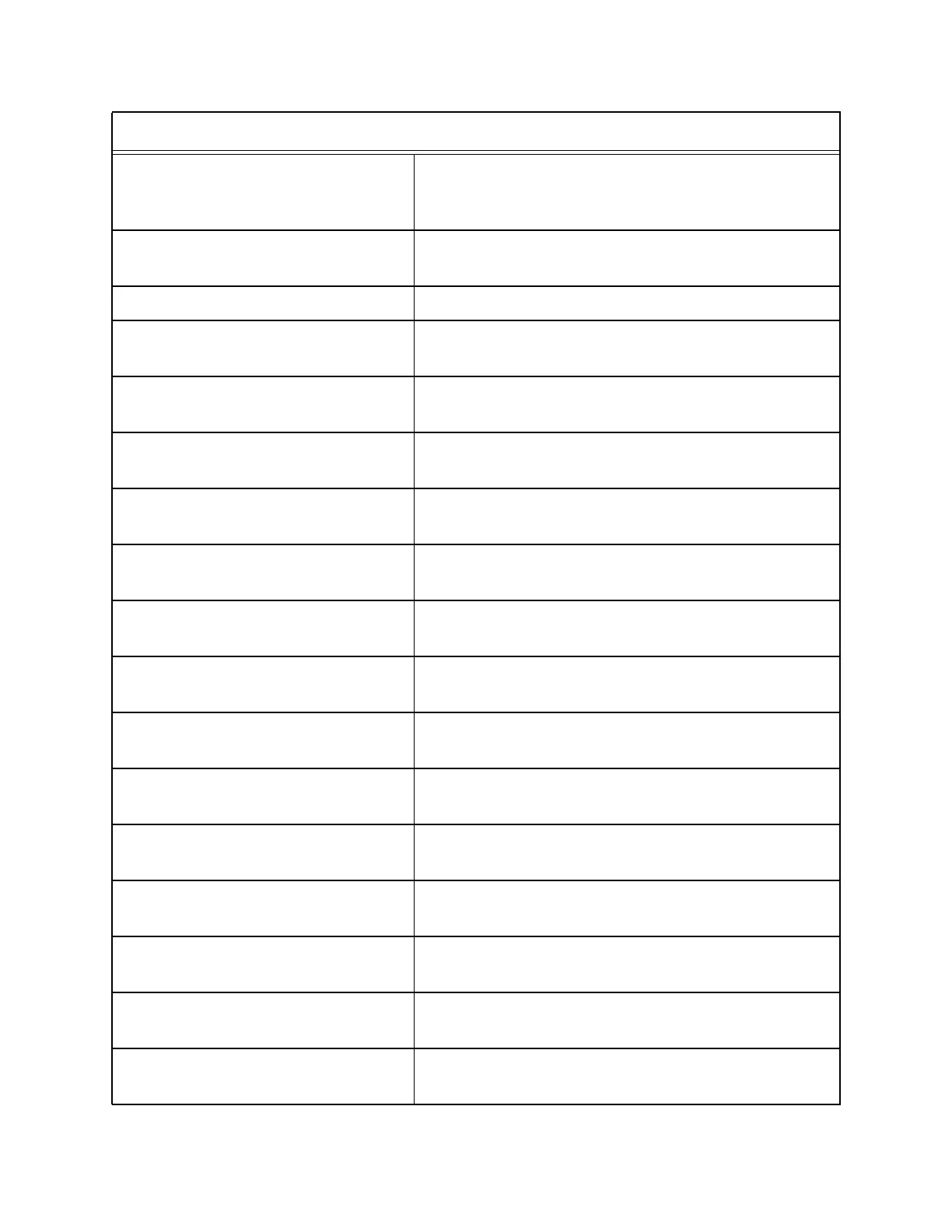

ADDS [R+], #data4 Add a short value to an indirect offset address,

with the indirect pointer automatically

incremented.

ADDS [R+offset8/16], #data4 Add a short value to an indirect offset address

(with 8 or 16-bit offset).

ADDS direct, #data4 Add a short value to a direct address.

MOVS ..., #data4 Move short data to destination using any of the

same addressing modes as ADDS.

ASL R, R Arithmetic shift left a byte, word, or double word,

up to 31 places, shift count read from register.

ASR R, R Arithmetic shift right a byte, word, or double word,

up to 31 places, shift count read from register.

LSR R, R Logical shift right a byte, word, or double word,

up to 31 places, shift count read from register.

ASL R, #DATA4/5 Arithmetic shift left a byte, word, or double word,

up to 31 places, shift count read from instruction.

ASR R, #DATA4/5 Arithmetic shift right a byte, word, or double word,

up to 31 places, shift count read from instruction.

LSR R, #DATA4/5 Logical shift right a byte, word, or double word,

up to 31 places, shift count read from instruction.

DIV R, R Signed divide of 32 bits register by 16 bit register,

or 16 bit register by 8 bit register.

DIVU R, R Unsigned divide of 32 bit register by 16 bit

register, or 16 bit register by 8 bit register.

MUL R, R Signed multiply of 16 bit register by 16 bit

register, or 8 bit register by 8 bit register.

MULU R, R Unsigned multiply of 16 bit register by 16 bit

register.

DIV R, #data8/16 Signed divide of 32 bits register by 16 bit

immediate, or 16 bit register by 8 bit immediate.

DIVU R, #data8/16 Unsigned divide of 32 bit register by 16 bit

immediate, or 16 bit register by 8 bit immediate.

MUL R, #data8/16 Signed multiply of 16 bit register by 16 bit

immediate, or 8 bit register by 8 bit immediate.

Table 9.3: Instructions and addressing modes new to the XA

New Instructions and Addressing Modes

Loading...

Loading...