XA User Guide 9-14 3/24/97

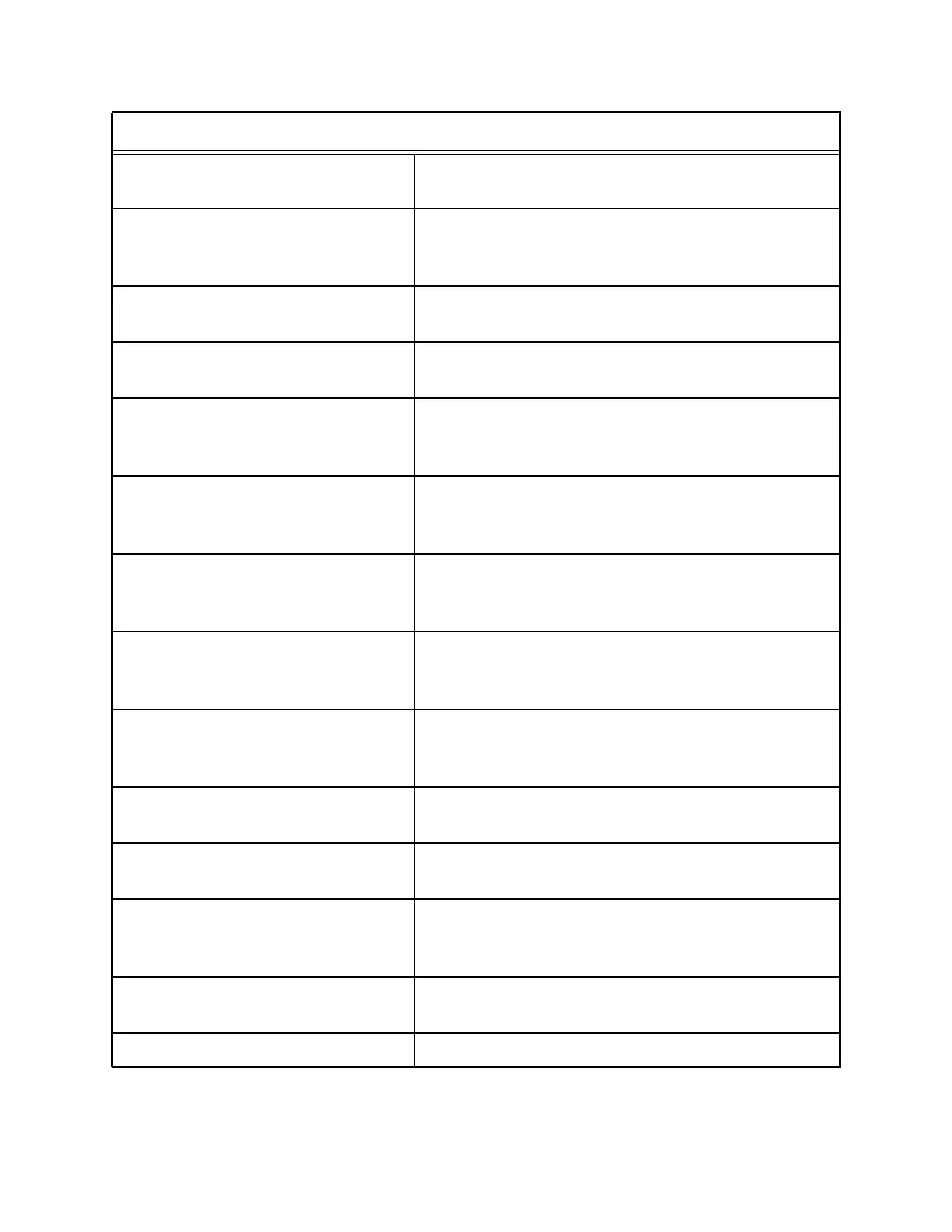

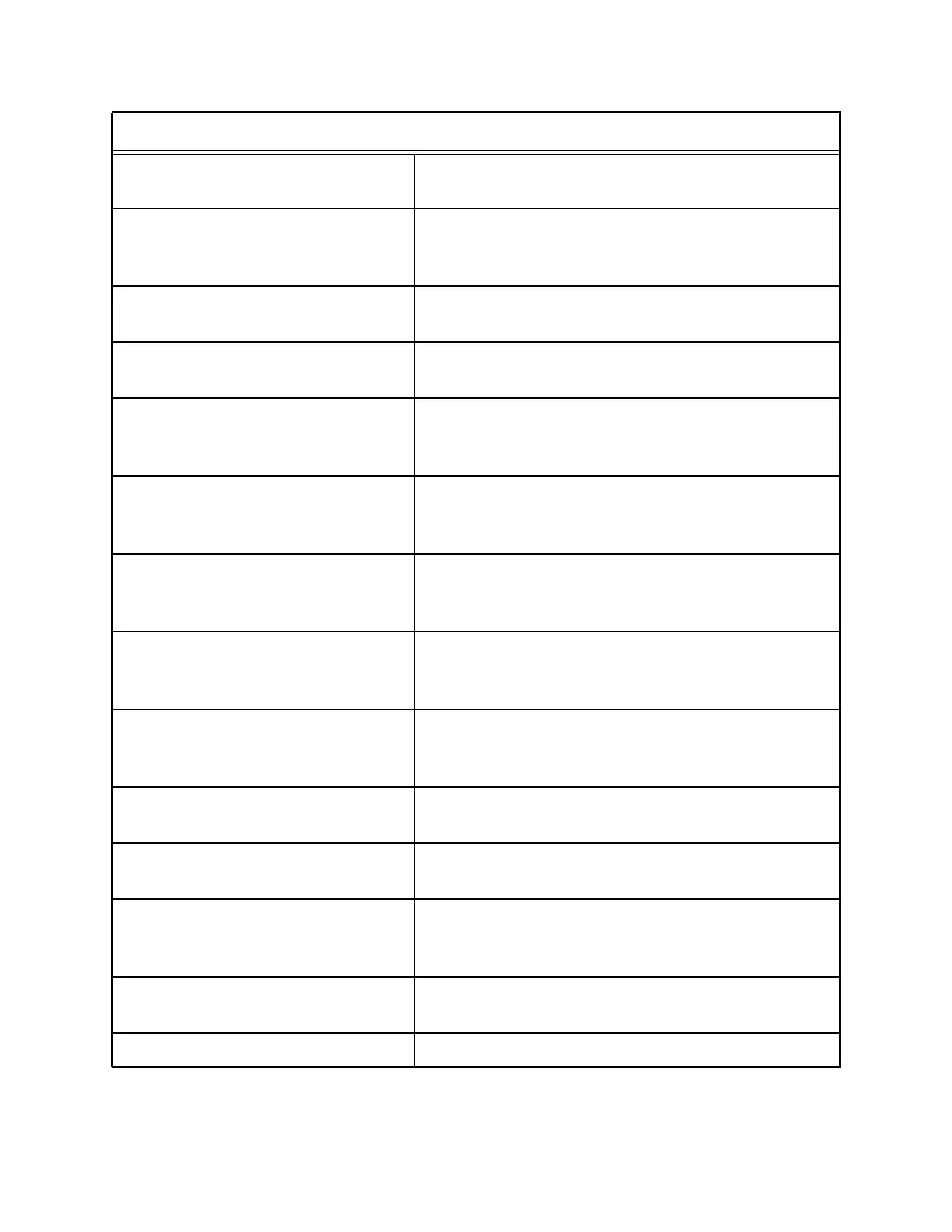

MULU R, #data8/16 Unsigned multiply of 16 bit register by 16 bit

immediate, or 8 bit register by 8 bit immediate.

LEA R, R+offset8/16 Load effective address, duplicates the offset8 or

16-bit addressing mode calculation but saves the

address in a register.

NEG R Negate, performs a twos complement operation

on a register.

SEXT R Sign extend, copies the sign flag from the last

operation into an 8 or 16-bit register.

NORM R, R Normalize. Shifts a byte, word, or double word

register left until the MSB becomes a 1. The

number of shifts used is stored in a register.

RL, RR, RLC, RRC R,#data4 All of the 80C51 rotate modes with 16-bit data

size and a variable number of bit positions (up to

15 places).

MOV [R+], [R+] Block move. Move data from an indirect address

to another indirect address, incrementing both

pointers.

MOV R, USP and USP, R Allows system code to move a value to or from

the user stack pointer. Handy in multi-tasking

applications.

MOVC R, [R+] Move data from an indirect address in the code

space to a register, with the indirect pointer

automatically incremented.

PUSH and POP Rlist PUSH and POP up to 8 word registers in one

instruction.

PUSHU and POPU Rlist or direct Allows system code to write to or read the user

stack. Handy in multi-tasking applications.

conditional branches A complete set of conditional branches, including

BEQ, BNE, BG, BGE, BGT, BL, BLE, BMI, BPL,

BNV, and BOV.

CALL [R] Call indirect, to an address contained in a

register.

CALL rel16 Call anywhere in a +/- 64K range.

Table 9.3: Instructions and addressing modes new to the XA

New Instructions and Addressing Modes

Loading...

Loading...