80C32/80C52

Rev. G (14 Jan. 97)

18

MATRA MHS

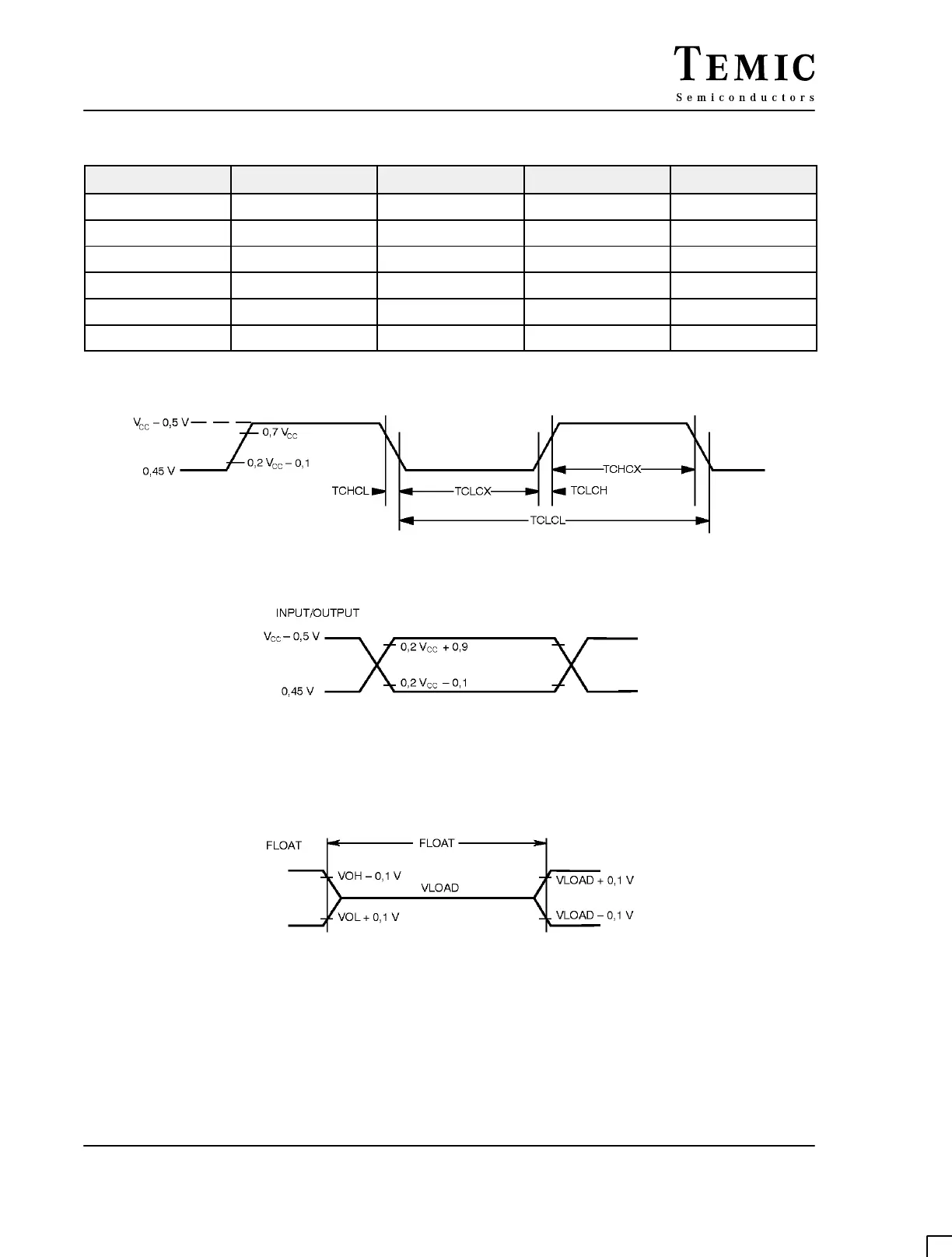

External Clock Drive Characteristics (XTAL1)

SYMBOL PARAMETER MIN MAX UNIT

FCLCL Oscillator Frequency 44 MHz

TCLCL Oscillator period 22.7 ns

TCHCX High Time 5 ns

TCLCX Low Time 5 ns

TCLCH Rise Time 5 ns

TCHCL Fall Time 5 ns

External Clock Drive Waveforms

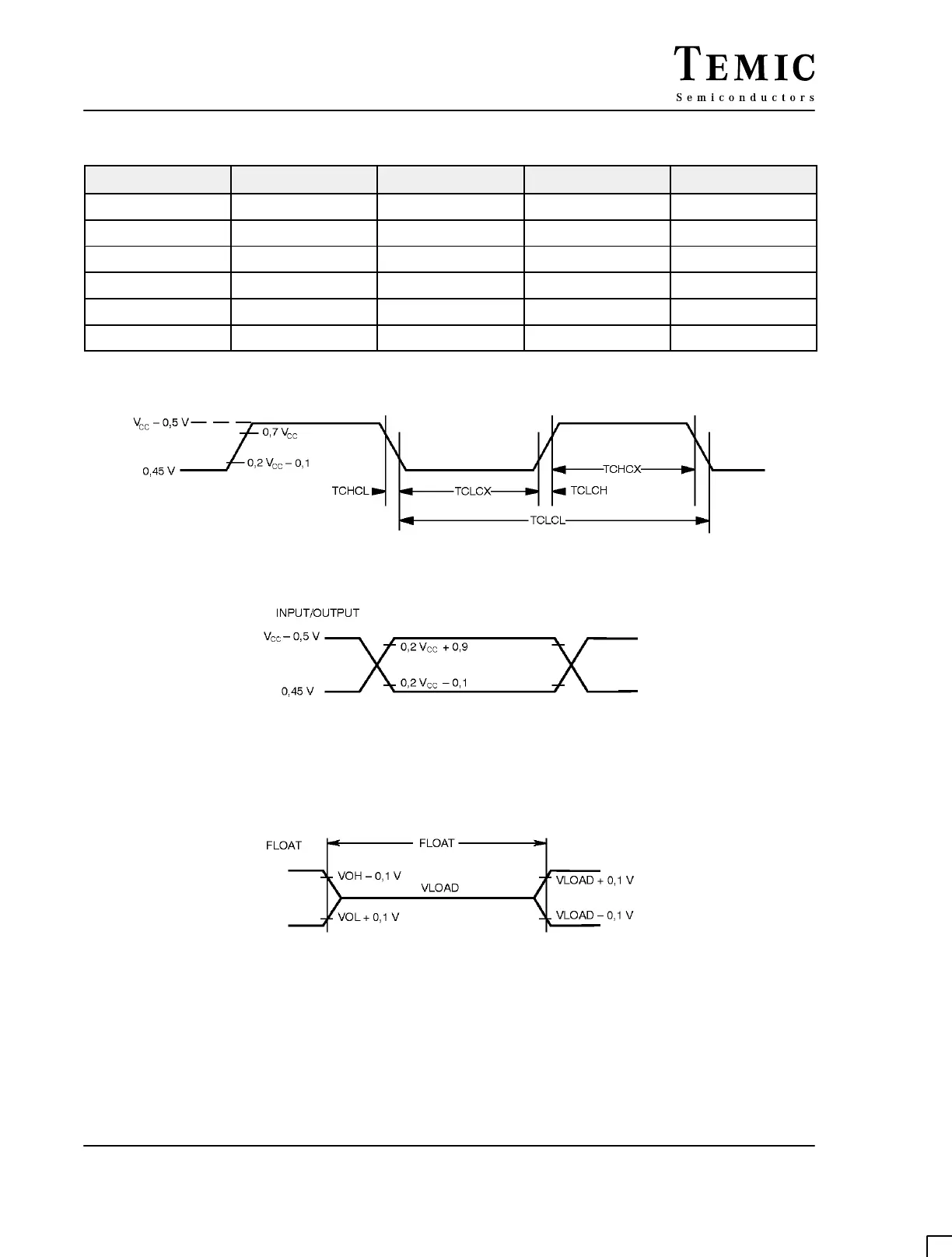

AC Testing Input/Output Waveforms

AC inputs during testing are driven at Vcc – 0.5 for a logic “1” and 0.45 V for a logic “0”. Timing measurements are

made at VIH min for a logic “1” and VIL max for a logic “0”.

Float Waveforms

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to

float when a 100 mV change from the loaded VOH/VOL level occurs. Iol/IoH ≥ ± 20 mA.

Loading...

Loading...