4-16

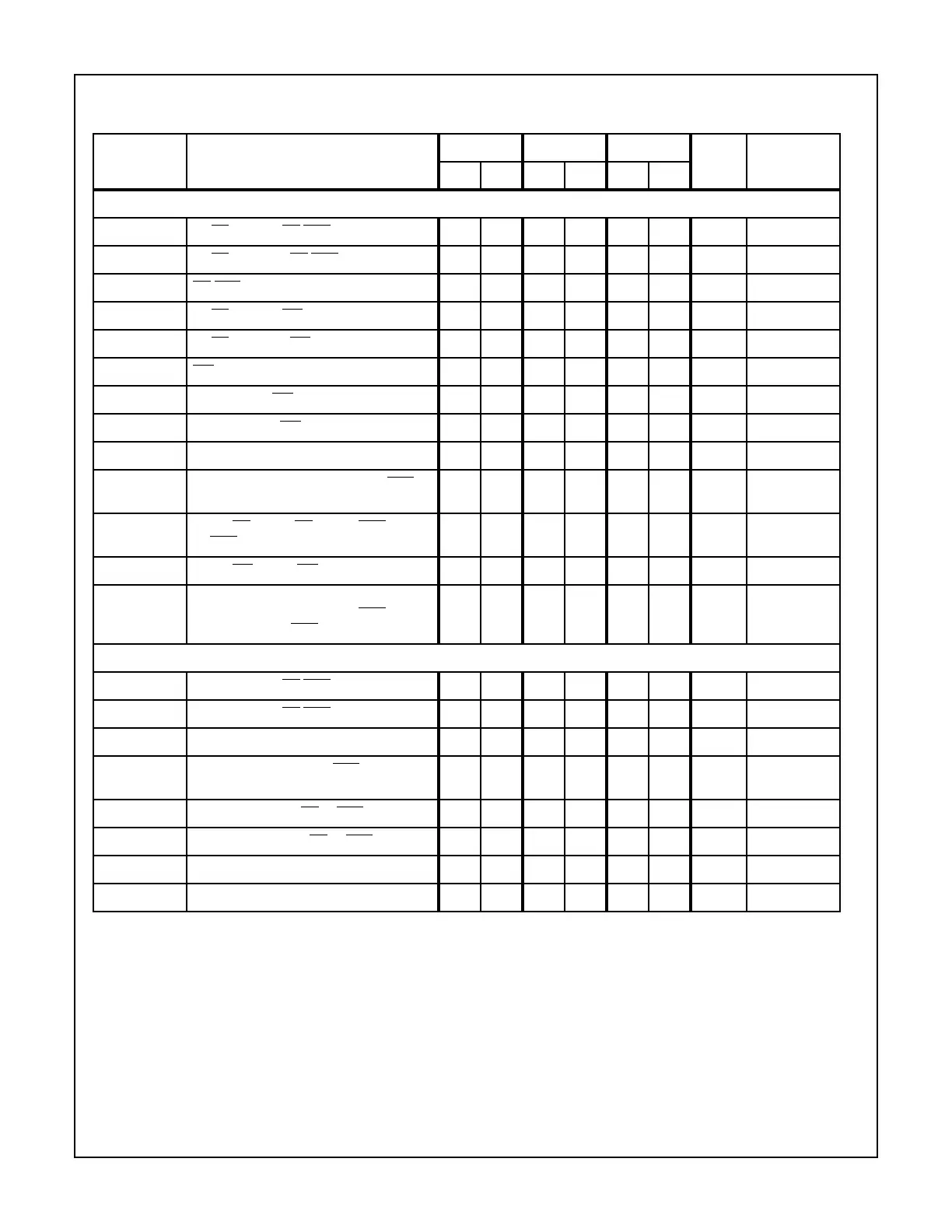

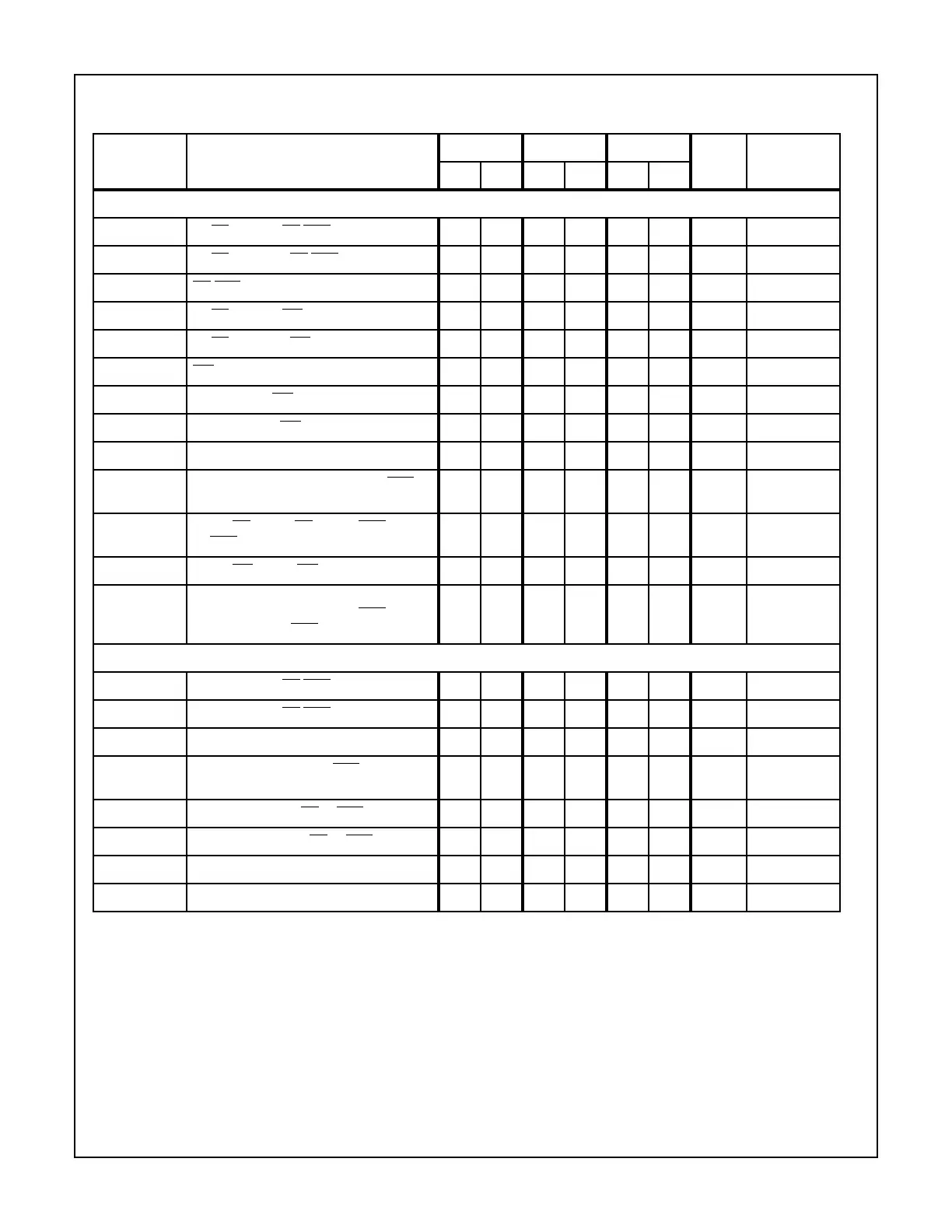

AC Electrical Specifications V

CC

= +5.0V ±10%, GND = 0V, T

A

= 0

o

C to +70

o

C (C82C59A), T

A

-40

o

C to +85

o

C (l82C59A),

T

A

= -55

o

C to +125

o

C (M82C59A)

SYMBOL PARAMETER

82C59A-5 82C59A 82C59A-12

UNITS

TEST

CONDITIONSMIN MAX MIN MAX MIN MAX

TIMING REQUIREMENTS

(1) TAHRL A0/CS Setup to RD/INTA 10 - 10 - 5 - ns

(2) TRHAX A0/CS Hold after RD/INTA 5-5-0- ns

(3) TRLRH RD/lNTA Pulse Width 235 - 160 - 60 - ns

(4) TAHWL A0/CS Setup to WR 0-0-0- ns

(5) TWHAX A0/CS Hold after WR 5-5-0- ns

(6) TWLWH WR Pulse Width 165 - 95 - 60 - ns

(7) TDVWH Data Setup to WR 240 - 160 - 70 - ns

(8) TWHDX Data Hold after WR 5-5-0- ns

(9) TJLJH Interrupt Request Width Low 100 - 100 - 40 - ns

(10) TCVlAL Cascade Setup to Second or Third INTA

(Slave Only)

55 - 40 - 30 - ns

(11) TRHRL End of RD to next RD, End of INTA (within

an INTA sequence only)

160 - 160 - 90 - ns

(12) TWHWL End of WR to next WR 190 - 190 - 60 - ns

(13) TCHCL

(Note 1)

End of Command to next command (not

same command type), End of INTA

sequence to next INTA sequence

500 - 400 - 90 - ns

TIMING RESPONSES

(14) TRLDV Data Valid from RD/INTA - 160 - 120 - 40 ns 1

(15) TRHDZ Data Float after RD/INTA 5 100 5 85 5 22 ns 2

(16) TJHlH Interrupt Output Delay - 350 - 300 - 90 ns 1

(17) TlALCV Cascade Valid from First INTA

(Master Only)

- 565 - 360 - 50 ns 1

(18) TRLEL Enable Active from RD or INTA - 125 - 100 - 40 ns 1

(19) TRHEH Enable Inactive from RD or INTA - 60 - 50 - 22 ns 1

(20) TAHDV Data Valid from Stable Address - 210 - 200 - 60 ns 1

(21) TCVDV Cascade Valid to Valid Data - 300 - 200 - 70 ns 1

NOTE:

1. Worst case timing for TCHCL in an actual microprocessor system is typically greater than the values specified for the 82C59A,

(i.e. 8085A = 1.6µs, 8085A -2 = 1µs, 80C86 = 1µs, 80C286 -10 = 131ns, 80C286 -12 = 98ns).

82C59A

Loading...

Loading...