Although a device can assert an interrupt at any time, the CPU usually only services (or

recognizes) interrupts between instructions. In other words, it does not stop in the middle of the

fetch/execute cycle to service an interrupt. This means there may be a delay between the time a

device generates an interrupt and the time the CPU processes it. We can expand the normal

fetch/execute cycle as follows:

Repeat

fetch instruction

decode instruction

fetch any memory operand necessary

execute instruction operation

write result to memory if necessary

check for hardware interrupt

Until Halt

Prioritizing Interrupts

The order in which the CPU checks devices with the polling scheme imposes a priority scheme

on the devices. Devices that the CPU checks first have a higher priority (they are more likely to

receive service). Imagine that two or more devices require service at the same time. The CPU

will service the device that it checks first before it services a device that it checks later. There is

also a priority scheme for interrupts, that is, the CPU considers some interrupt requests to be

more important than others.

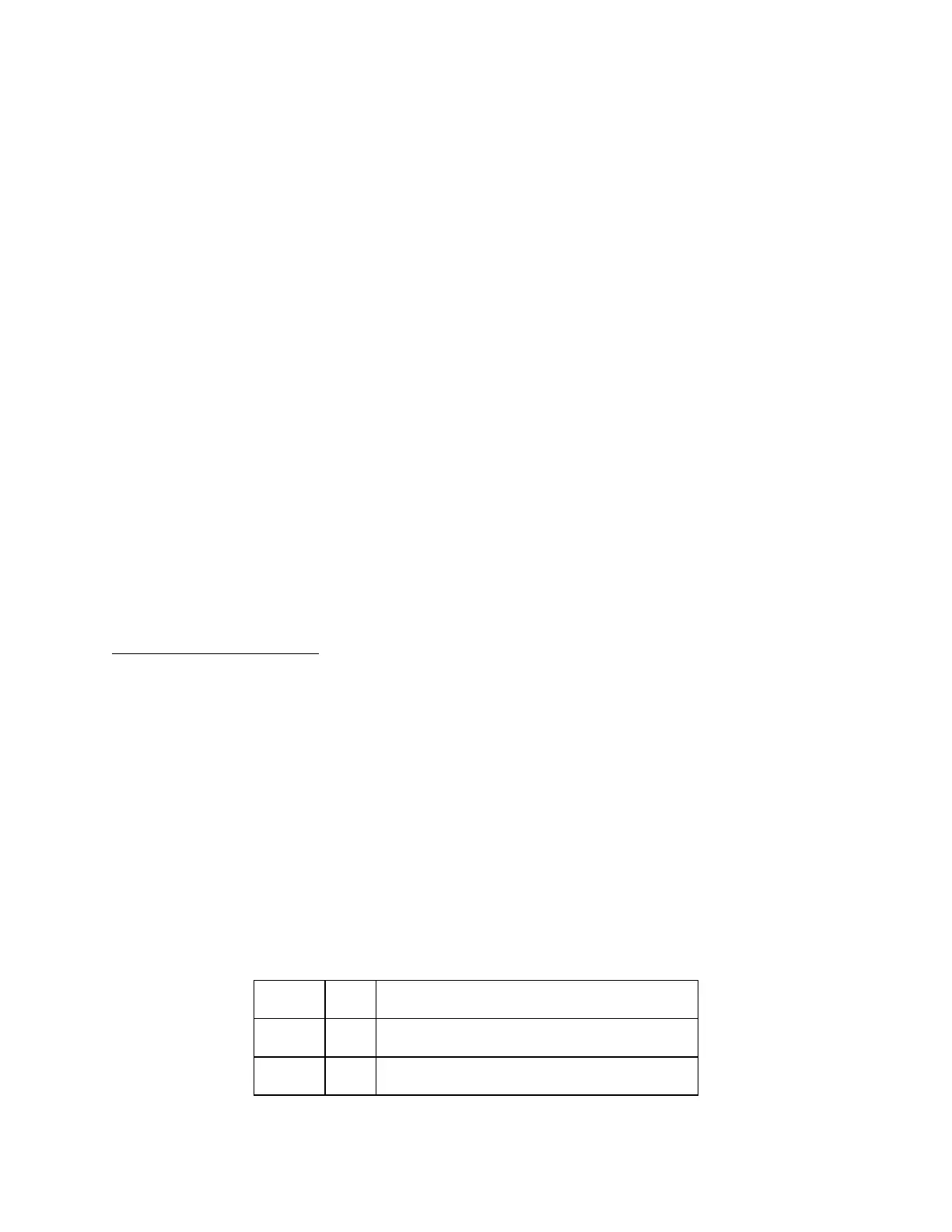

Intel Interrupt Prioritization

The implementation of this prioritization is as follows. First, it is important to understand that

peripheral devices do not connect directly to the CPU. Instead, an interrupt controller (the

8259A chip) stands between the devices and the processor. This controller is a hardware device

that receives signals from up to eight different external devices. The chip has eight input lines,

each of which can connect to a peripheral device. The names of these input lines, IRQ0-IRQ7

(Interrupt ReQuest), correspond to the relative priorities of the devices attached to them, with the

device attached to line IRQ0 having the highest priority. The table below shows the standard

IRQ assignments. A device that requires the attention of the processor sends a signal on its line

to the interrupt controller. At any given moment, all, some, or none of the devices may require

the services of the CPU. If more than one device is sending a signal at the same time, the

controller selects the line with the highest priority (lowest numbered) of all the lines currently

active. Only the device connected to this line will actually be able to get the attention of the

CPU. The 8259A encodes the vector number corresponding to the selected signal and stores this

value in an internal register of the controller itself.

Priority IRQ Device

highest 0 System timer

1 Keyboard

Loading...

Loading...