CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

32 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

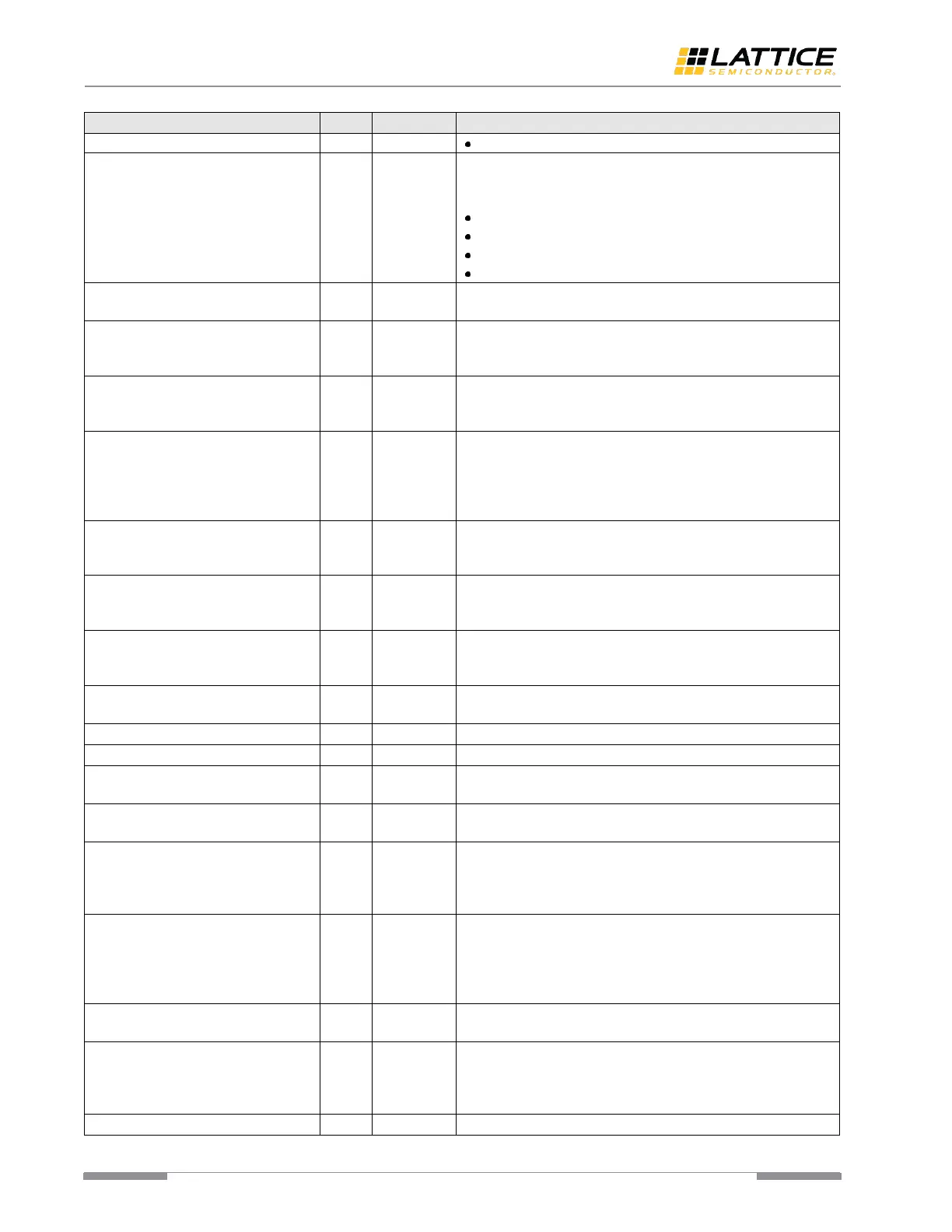

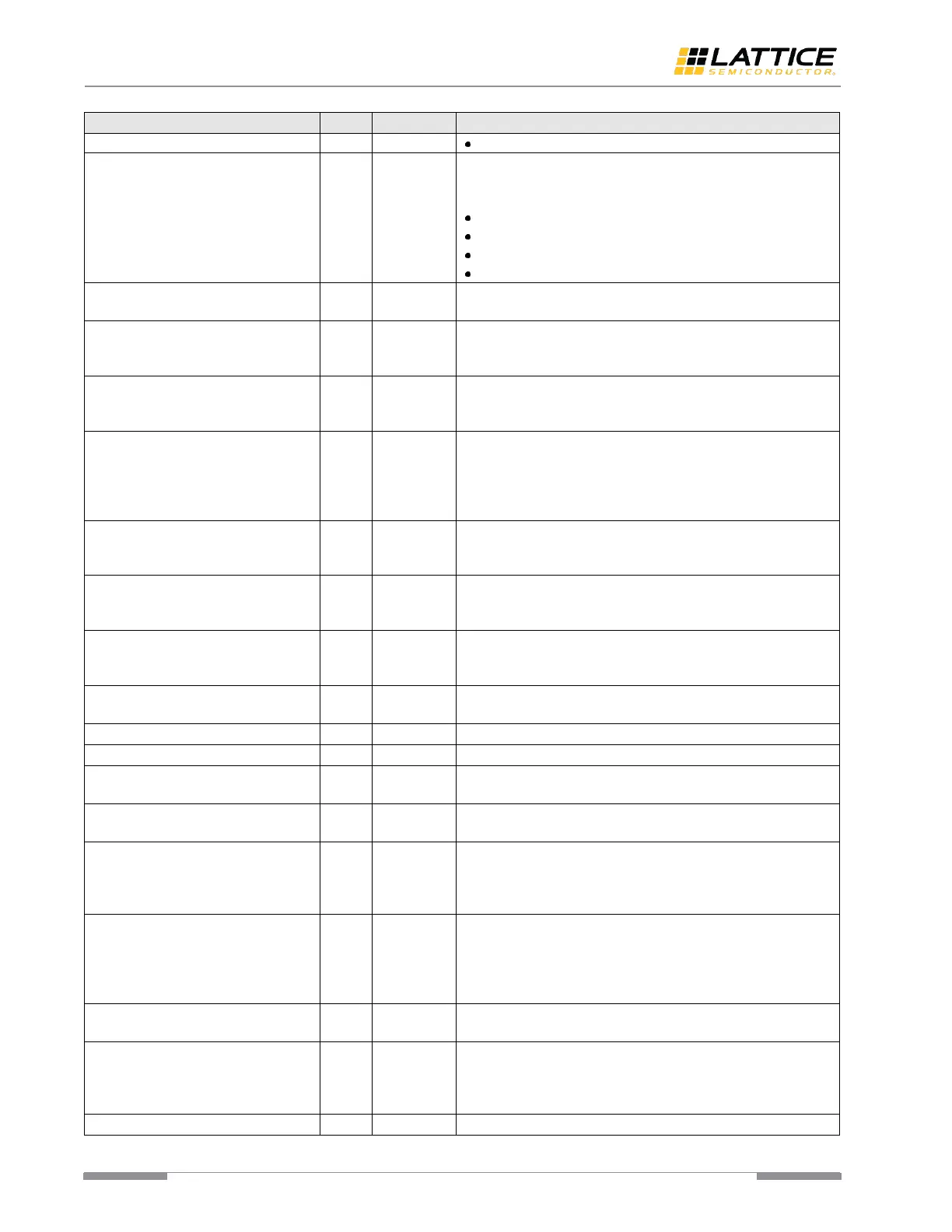

Powerdown. This is a per-lane signal.

pipe_powerdown_i[1:0] = power state driving by the

PCI-Express controller:

2’b11 – P2

2’b10 – P1

2’b01 – P0s

2’b00 – P0

This signal is a per-lane signal which is generated by the PHY

macro for each lane of the PCI-Express controller.

TxdetectRx/Loopback. This signal is a per-link signal which is

generated by each link PCI-Express controller. The PCS logic

performs the internal mapping of link to lanes.

Transmit de-emphasis. This signal is a per-link signal which is

generated by each link PCI-Express controller. The PCS logic

performs the internal mapping of link to lanes.

Transmit margin. This signal is used at 5 Gbps or 8 Gbps speed

by the MAC in order to control the PHY settings in term of

amplitude, de-emphasis. This signal is a per-link signal which is

generated by each link PCI-Express controller. The PCS logic

performs the internal mapping of link to lanes.

Transmit swing. This signal is a per-link signal which is generated

by each link PCI-Express controller. The PCS logic performs the

internal mapping of link to lanes.

Transmit data. CI-Express controller. The width of this signal can

be 8 bits or 16 bits per lane depending on whether PIPE16BIT is

defined or not.

Transmit control character. This signal is a per-lane signal. The

width of this signal can be 1 bit, 2 bits or 4 bits per lane,

depending on whether PIPE16BIT or PIPE32BIT is defined or not.

Transmit data valid. The PCS logic performs the internal

mapping of link to lanes

Transmit data starting byte.

Transmit electrical idle. This signal is a per-lane signal which is

generated by each link PCI-Express controller.

Transmit compliance. This signal is a per-lane signal which is

generated by each link PCI-Express controller.

Receive data. This signal is a per-lane signal which is generated

by the PHY macro for the PCI-Express controller. The width of

this signal can be 8 bits, 16 bits or 32 bits per lane, depending

on whether PIPE16BIT or PIPE32BIT is defined or not.

Receive control character. This signal is a per-lane signal which

is generated by the PCI-Express PHY for the PCI-Express

controller. The width of this signal can be 1 bit, 2 bits or 4 bits

per lane, depending on whether PIPE16BIT or PIPE32BIT is

defined or not.

Receive data valid. This signal is a per-lane signal which is

generated by the PHY macro for the PCI-Express controller.

Receive data starting byte. This signal allows the PHY to tell the

MAC the starting byte for 128-bit block. This signal is a per-lane

signal which is generated by the PHY macro for the PCI-Express

controller.

Receive sync header bits. This signal reports the content of the

Loading...

Loading...