Network and Remote Operation

R&S

®

FSVA3000/ R&S

®

FSV3000

673User Manual 1178.8520.02 ─ 01

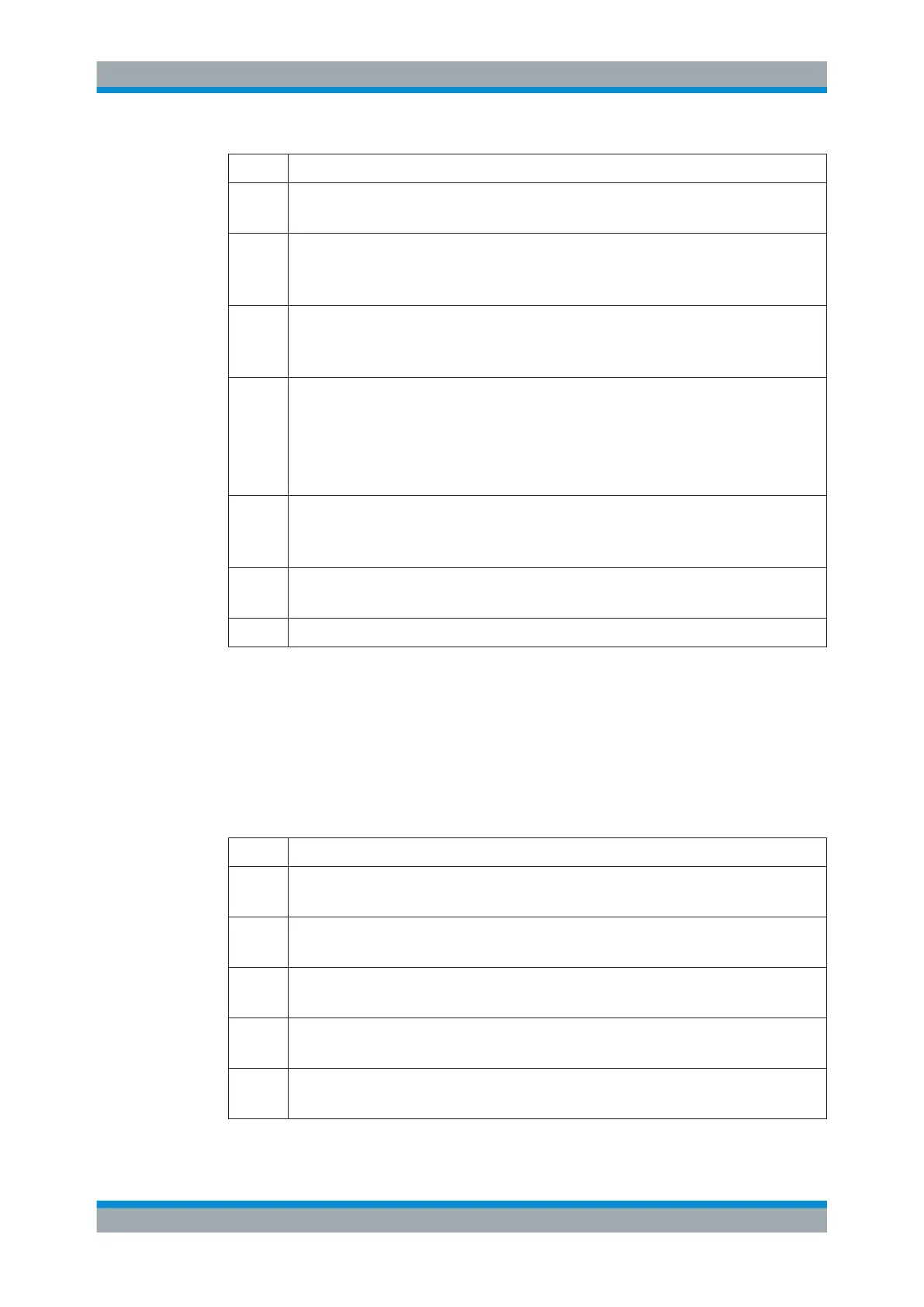

Bit No. Meaning

8 "CALibration"

This bit is set if the R&S FSV/A is unaligned ("UNCAL" display)

9 "LIMit" (device-specific)

This bit is set if a limit value is violated in any of the active channels in any window.

The STATus:QUEStionable:LIMit Register provides more information on the error type.

10 "LMARgin" (device-specific)

This bit is set if a margin is violated in any of the active channels in any window.

The STATus:QUEStionable:LMARgin Register provides more information on the error type.

11 "SYNC" (device-specific)

This bit is set if the R&S FSV/A is not synchronized to the signal that is applied.

The R&S FSV/A is not synchronized if:

●

it cannot synchronize to midamble during a measurement or premeasurement

●

it cannot find a burst during a measurement or premeasurement

●

the results deviate too much from the expected value during premeasurements

12 "ACPLimit" (device-specific)

This bit is set if a limit during ACLR measurements is violated in any of the active channels.

The STATus:QUEStionable:ACPLimit Register provides more information on the error type.

13

13-14

Unused

15 This bit is always 0.

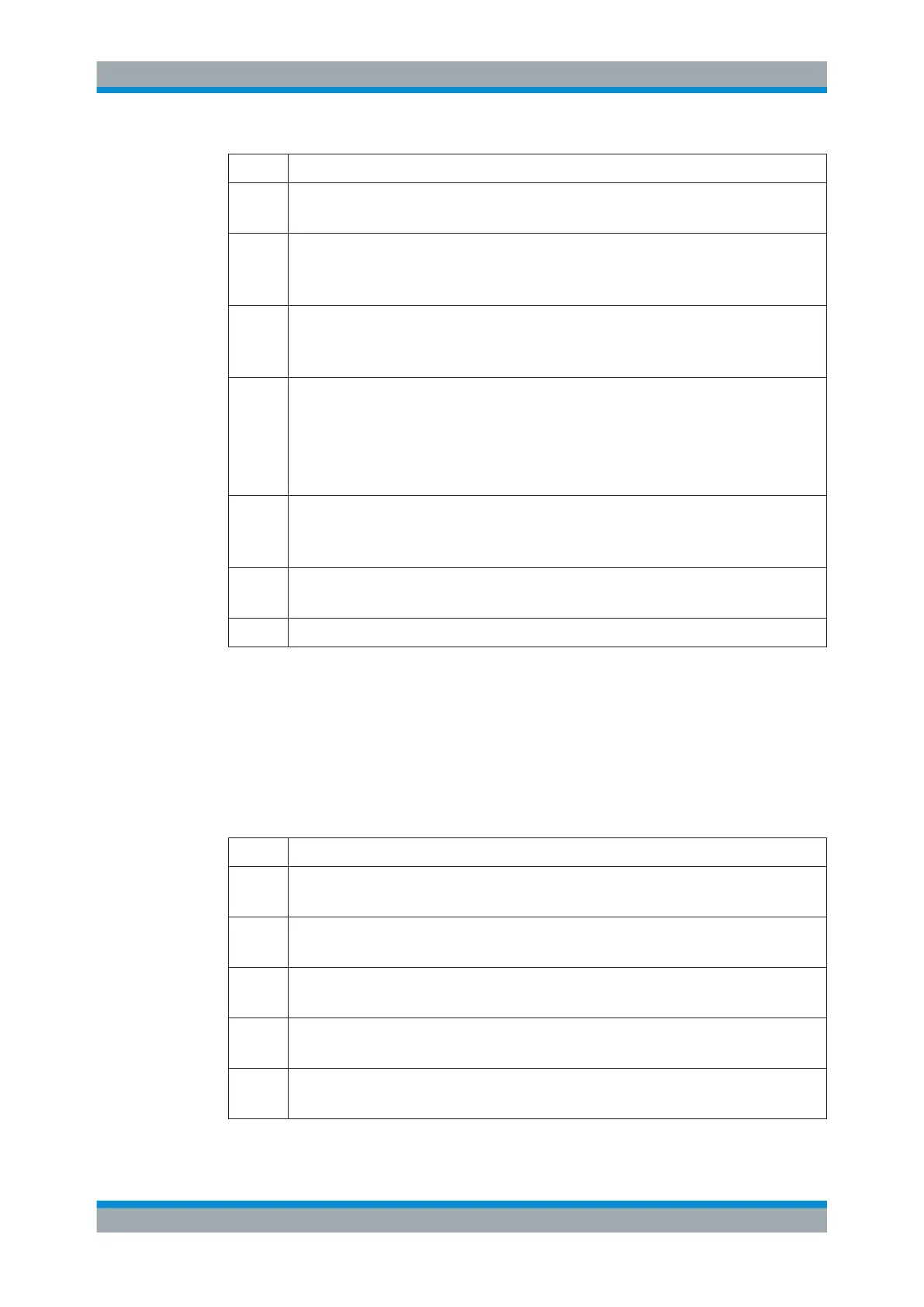

STATus:QUEStionable:ACPLimit Register

The STATus:QUEStionable:ACPLimit register contains information about the results of

a limit check during ACLR measurements. A separate ACPLimit register exists for

each active channel.

You can read out the register withSTATus:QUEStionable:ACPLimit:CONDition?

or STATus:QUEStionable:ACPLimit[:EVENt]?

Table 13-11: Meaning of the bits used in the STATus:QUEStionable:ACPLimit register

Bit No. Meaning

0 ADJ UPPer FAIL

This bit is set if the limit is exceeded in the upper adjacent channel

1 ADJ LOWer FAIL

This bit is set if the limit is exceeded in the lower adjacent channel.

2 ALT1 UPPer FAIL

This bit is set if the limit is exceeded in the upper 1st alternate channel.

3 ALT1 LOWer FAIL

This bit is set if the limit is exceeded in the lower 1st alternate channel.

4 ALT2 UPPer FAIL

This bit is set if the limit is exceeded in the upper 2nd alternate channel.

Remote Control Basics

Loading...

Loading...