6 — LP MDU, MDU, and modular ONT hardware functional blocks

Alcatel-Lucent 7342 ISAM FTTU ONT R04.05.06 July 2008 6-11

3FE 51892 AAAA TCZZA Edition 01 ONT Product Information Manual

A FPGA is required to provide the GPON MAC to Ethernet function. An Ethernet

switch provides the traffic interface between the GPON MAC and the VDSL2 chips.

A programmable logic device (PLD) is required to provide the interface between the

on-board controller (OBC) and the control interface of the VDSL2 chips.

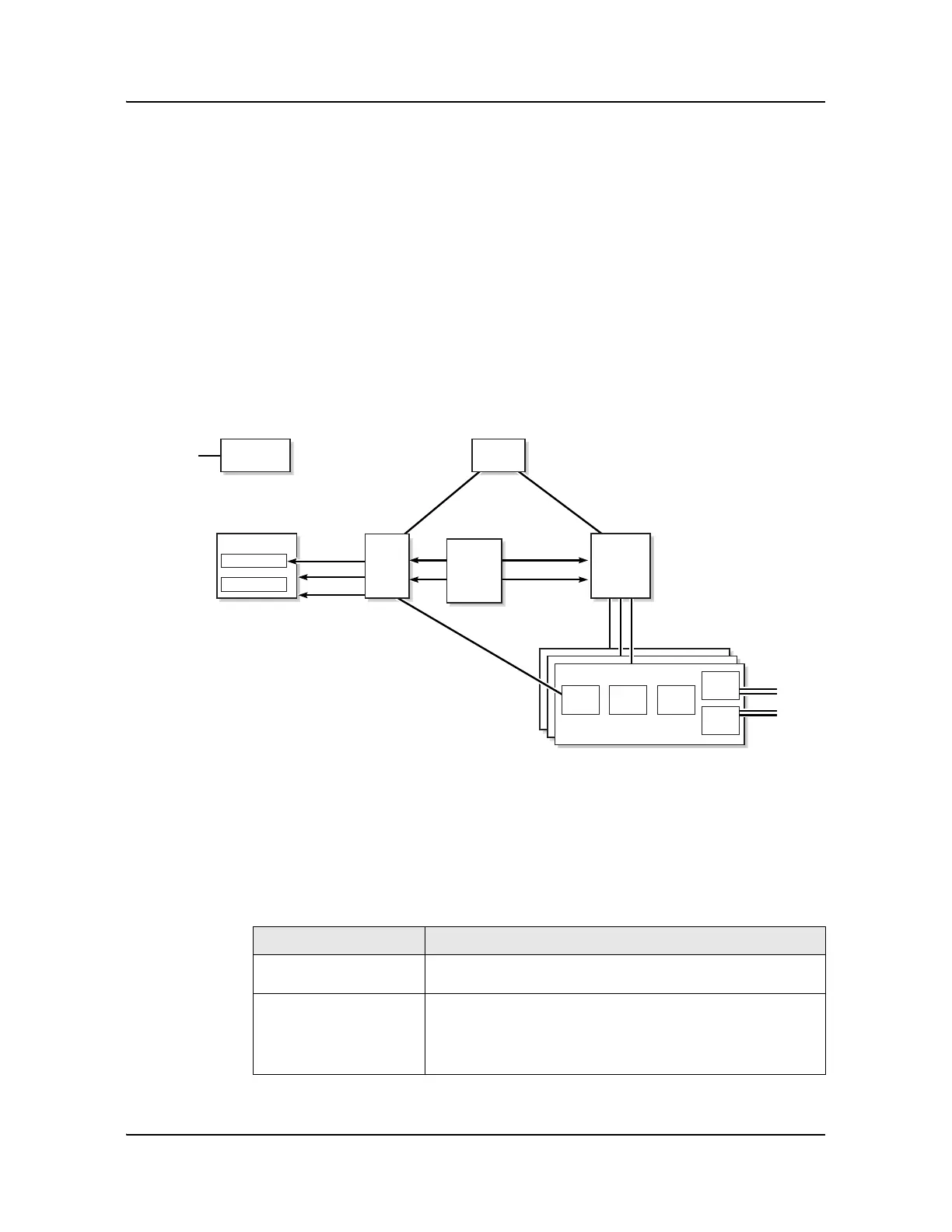

The O-00240V-A MDU ONT board contains the following functional blocks:

• Luminent diplexer

• GPON MAC FPGA

• Ethernet switch

• on-board controller

Figure 6-4 illustrates the functional block for the O-00240V-A MDU outdoor ONT.

Figure 6-4 O-00240V-A MDU ONT functional blocks

GPON MAC FPGA

The GPON MAC FPGA interacts with the Ethernet functions and provides GPON

MAC functions. Table 6-9 describes the features of the GPON MAC FPGA.

Table 6-9 GPON MAC FPGA features

Data

SS SMII

PCI

Bus

Control

Bus

Data

Clock

Diplexer

Serializer

Deserializer

-48 V power

Converter

OBC

HiGL 2.5G

1965

ENET 2.5G

SERDES

Ethernet

switch

24

VDSL

Ports

LD 2

CH

LD 2

CH

VDSL

IFE

(2x4 CH)

VDSL

AFE

(2x4 CH)(8 CH)

VDSL

BME

GPON

MAC

FPGA

Feature Description

Interfaces Supports two 2.5 Gigabit interfaces toward to the Ethernet switch as

well as the GPON interface.

Upstream and downstream

FEC

Supports 1.24.Gb/s upstream and 2.49 Gb/s downstream FEC. FEC is

a data encoding format used with data transmissions in the transport

layer between the MDU ONT and an P-OLT. The encoding introduces

redundancy, which allows the decoder to detect and correct the

transmission errors.

(1 of 2)

Loading...

Loading...