Chapter 3. 9500 MXC Nodes

Vol. II-3-46 Alcatel-Lucent

• Flow control through 802.3x pause-frame option;

• Frames sizes to 1536 bytes;

• Comprehensive RMON and performance indicators;

• Compatibility with the DAC GE (from SW release 3.6).

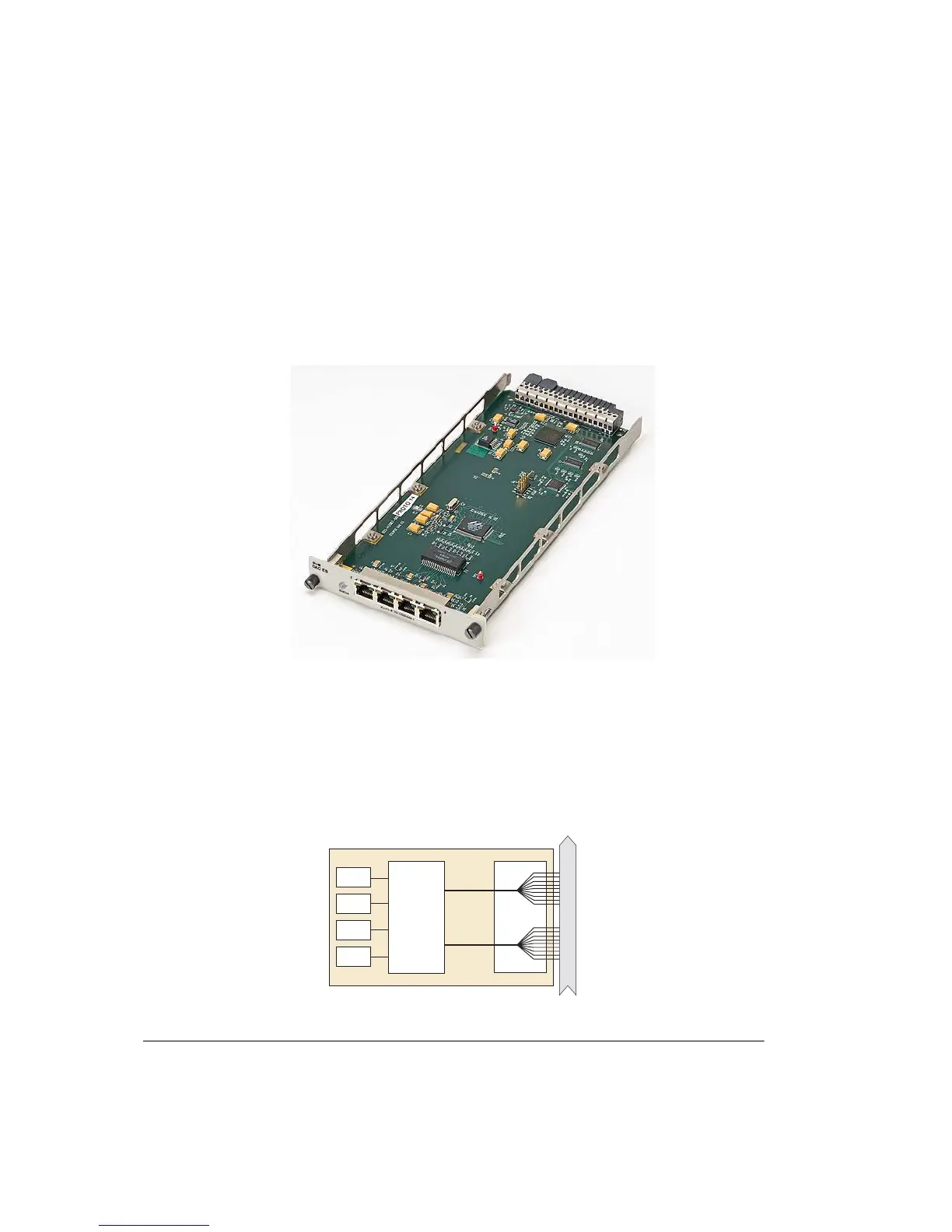

Figure 3-28. DAC ES Plug-in

Figure 3-29 illustrates basic operational blocks within the DAC ES. Four RJ-45

customer ports connect to an Ethernet switch, which provides the bridge/switch

and queueing functions between the ports and two transport channels. The gate

array (FPGA) provides signal framing and the interface to the backplane bus,

with software selection of the number of E1 or DS1 circuits (Ethernet data

capacity) used to transport the Ethernet traffic over each transport channel, which

may be on a RAC or DAC 155oM. The DAC ES MAC address register supports

4096 entries.

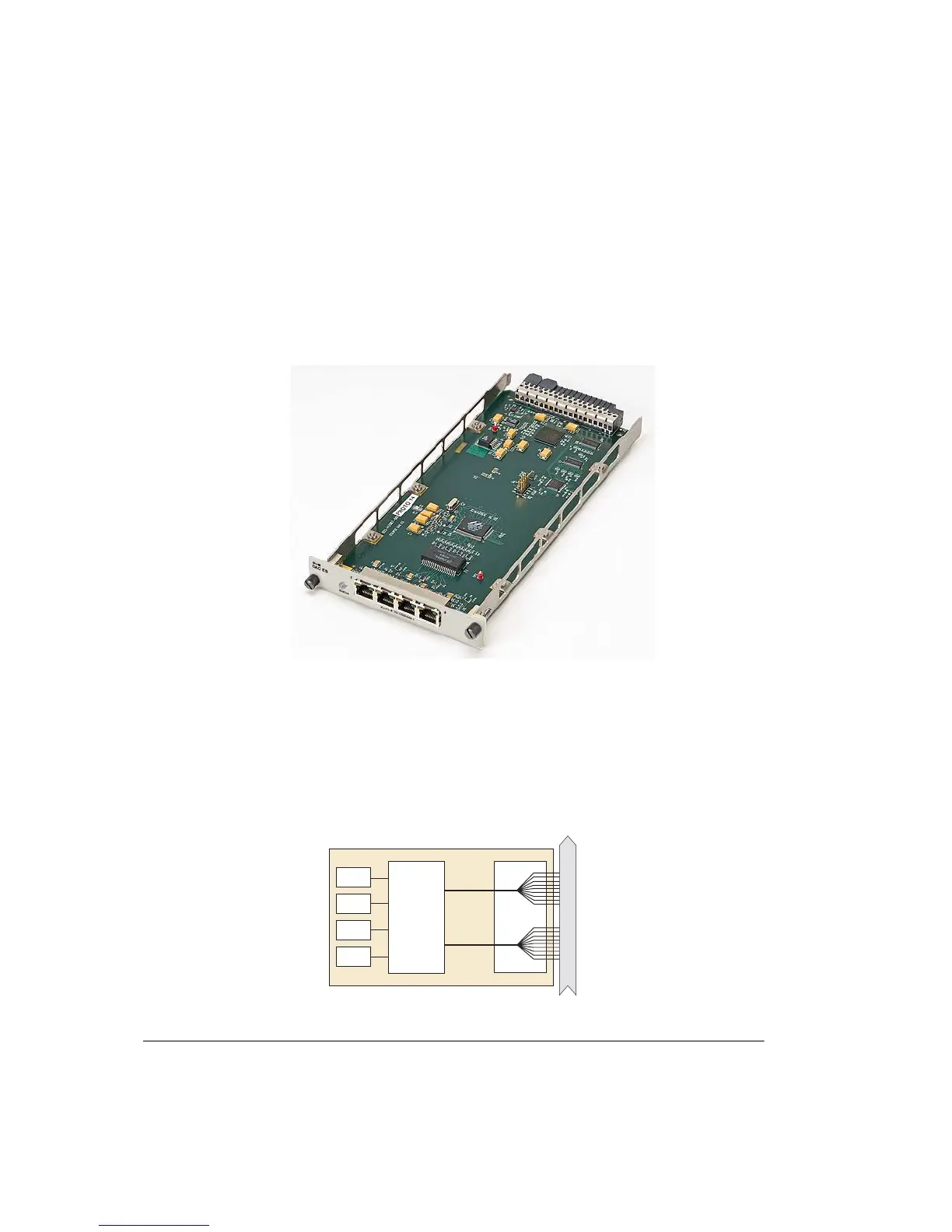

Figure 3-29. DAC ES Block Diagram

Port 1

Port 4

Port 3

Port 2

Ethernet

L2+ Switch

(Mode and

QoS engine)

C1

C2

Transport

Channels

FPGA

RJ-45

Ethernet

Ports

High Speed Bus

Loading...

Loading...