GR712RC-UM, Jun 2017, Version 2.9 21 www.cobham.com/gaisler

GR712RC

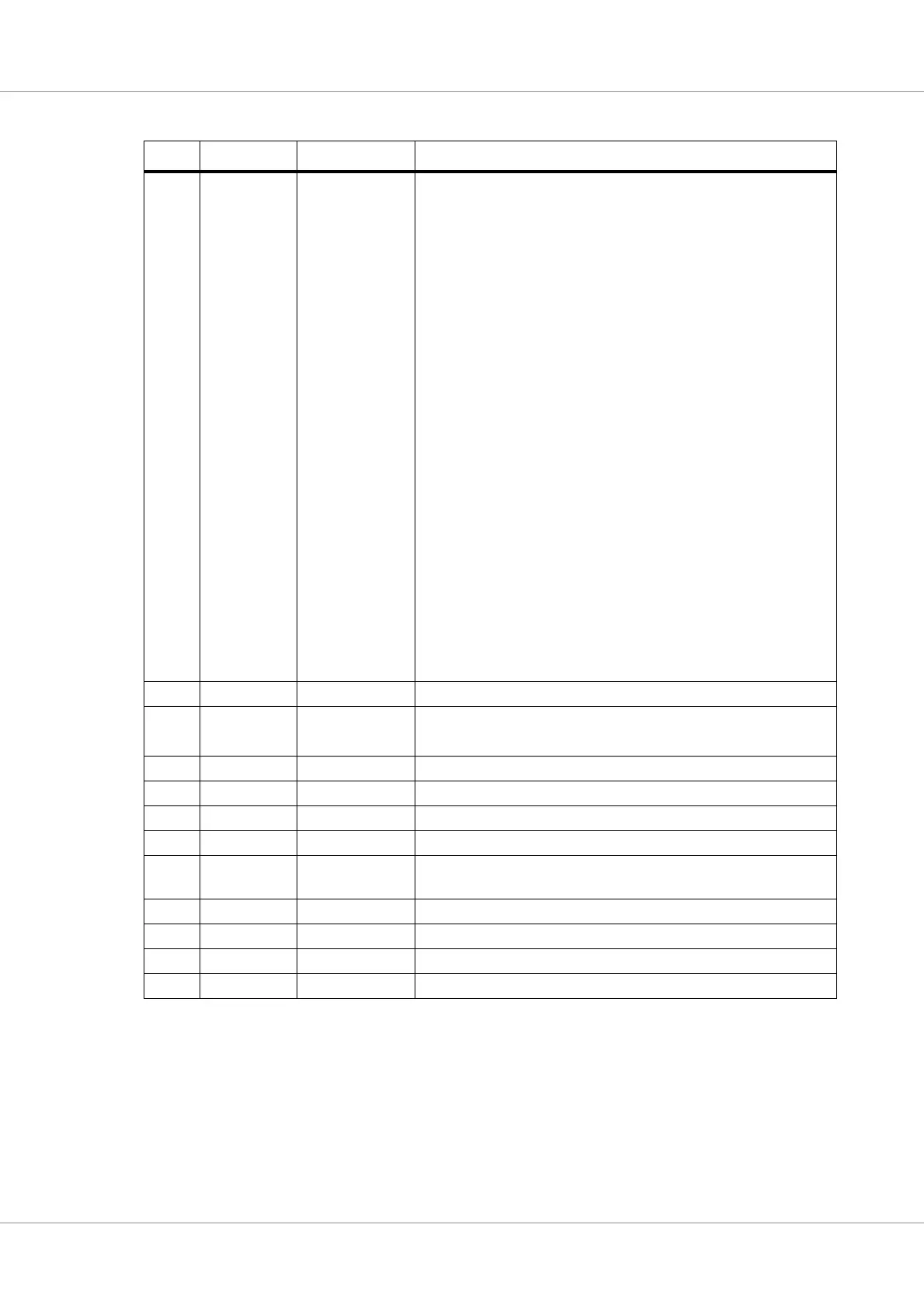

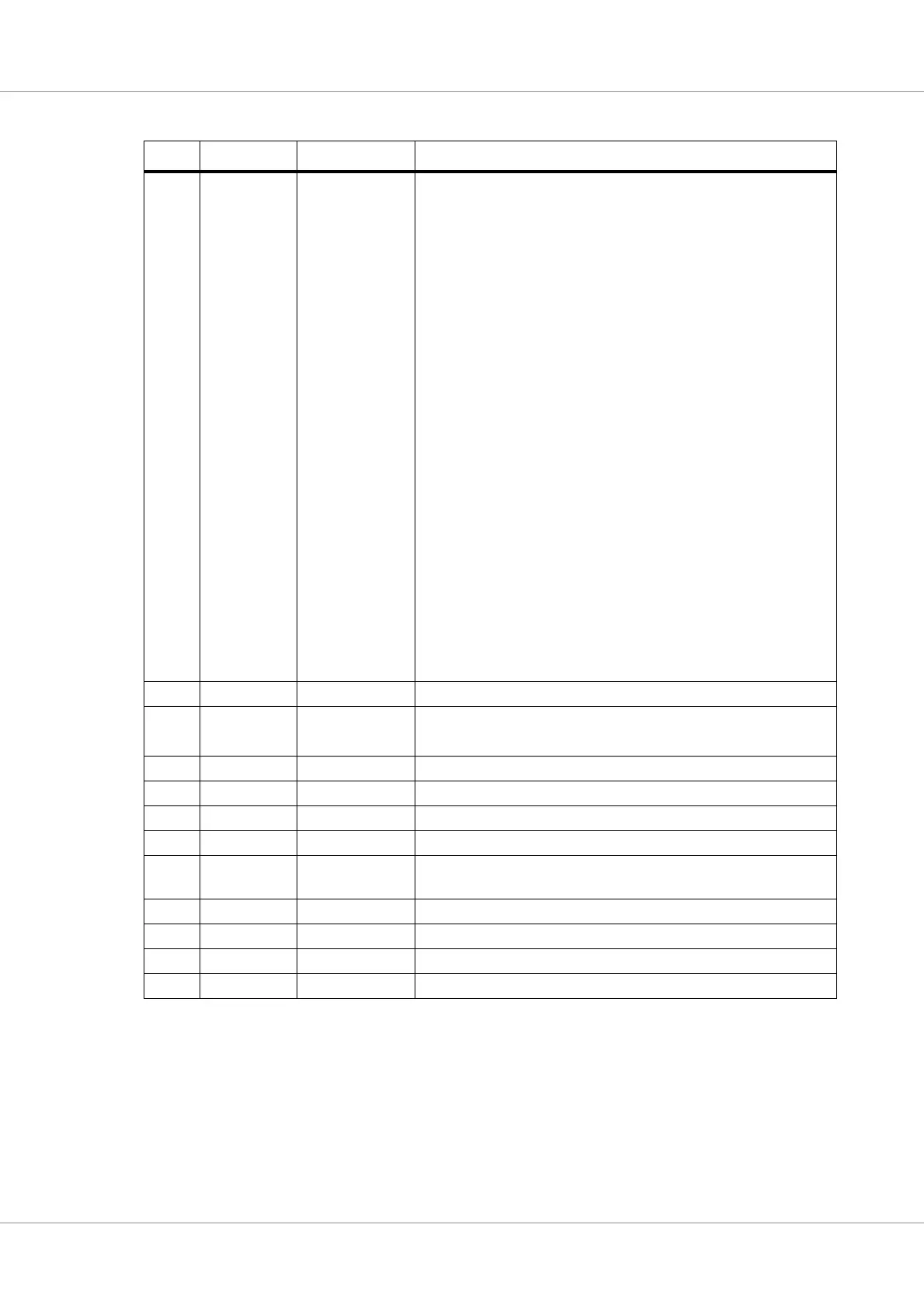

2.1 2012-12-21 1.3

1.7

2

4.2.16, 6.1

5

5.10.2

5.15

8.3

10.4

11.2

12.2

12.3

13.2

1.2, 16.1

16.4.8

16.9

18.3

21.4

23

Updated GRTC address mapping

Added errata section

Updated I/O switch matrix conflict table 8

On-chip memory is not cacheable

Added SRAM read-modify-write timing diagram and various

memory controller clarifications.

Clarified 8-bit EDAC limitation to a single bank

Clarified that busy ready signal also applies to PROM area

Clarified interrupt controller register definitions

Clarified handling of unused JTAG interface

Watchdog dependent on interrupt setting for timer

Clarified timer latching limitations

Corrected memory map

Typo in register definition

SpaceWire core configuration information added

SpaceWire read descriptor handling clarified

SpaceWire register reset values clarified

CAN register mapping corrected

Reset value of ssysfn bit corrected for Mil-Std-1553B core

Updated SPI controller capability register descriptions with

implemented values, removed functions not implemented.

2.0 2011-10-18 Clarifications, see change bars

1.9 2011-02-25

2010-11-09

Updated all sections with additional details

Corrected typos in address map

1.8 2010-07-30 Re-ordered chapters, improved description of clocking

1.7 2010-03-31 Refined text to describe only the GR712RC config

1.6 2009-06-23 Added GRTIMER, updated GRTM and IRQs

1.5 2009-05-19 Corrected bus timing register

1.4 2009-04-07 Added separate chapters for clocking and I/O switch matrix.

Updated GPREG, BRM.

1.3 2009-04-06 Added BTR registers and GPREG section

1.2 2009-04-01 Changes in clocking options

1.1 2009-03-09 Incorporated feedback from RC

1.0 2009-03-02 Initial specification

TABLE 4. Revision history

Issue Date Sections Description

Loading...

Loading...