160 b EDN S

EPTEMBER 24, 1998

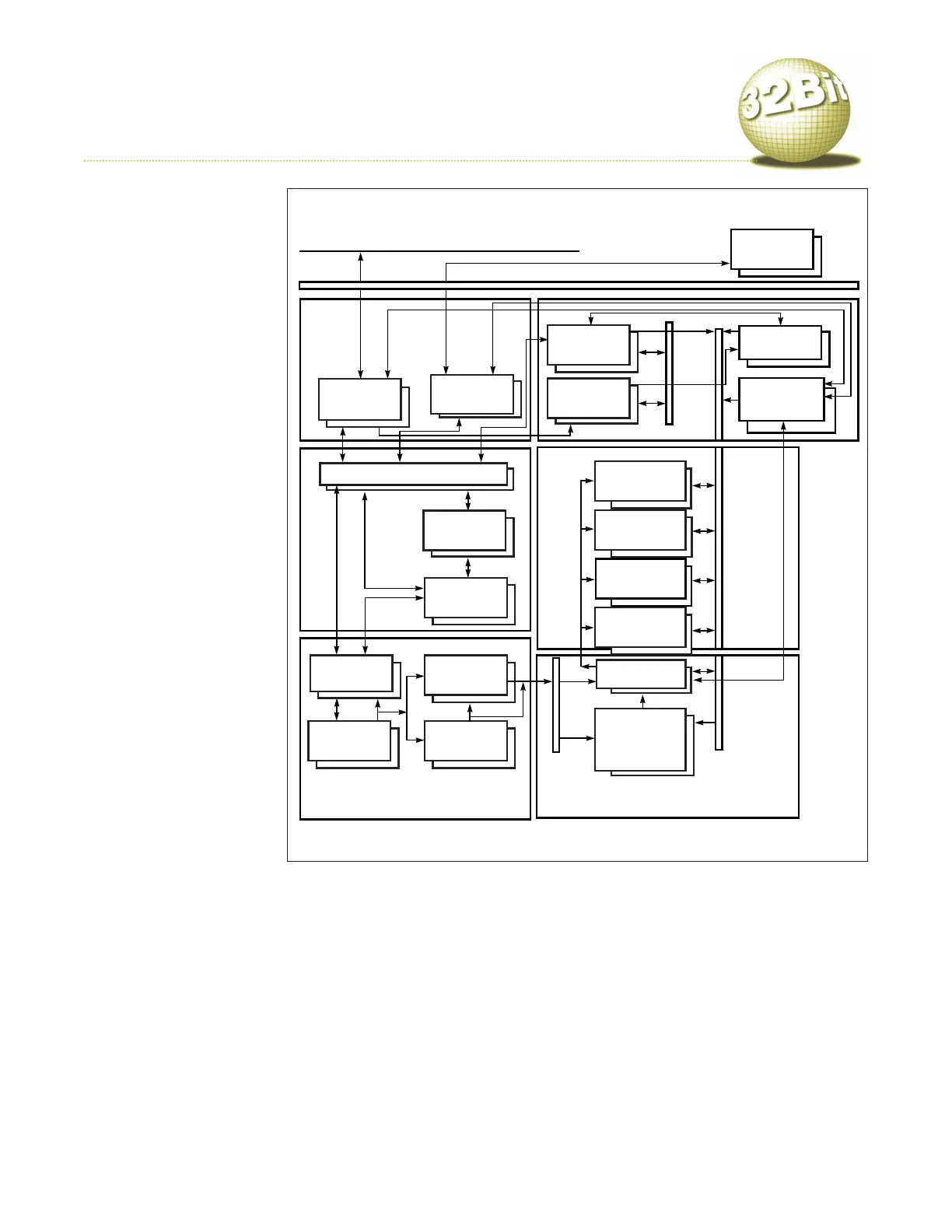

Because of Intel’s patent on

the Slot 1 processor’s CPU

interface, the company is the

sole source of these proces-

sors, primarily characterized

by their dedicated backside

L2-cache bus. Separate buses

to main memory and L2

cache allow the CPU to access

the L2 cache at 200 MHz,

one-half the core-processor

speed. Slot 1 provides Intel’s

GTL+ bus protocol, which is

helpful in multiprocessor sys

-

tems.

Intel’s Slot 1-compatible

Pentium II barely resembles

the Pentium or any other x86

processor. With a decoupled

12-stage pipeline, the Pen-

tium II trades less work per

pipe stage for more stages.

The Pentium II comprises

three independent engines:

fetch/decode, dispatch/exe-

cute, and retire. The fetch/

decode engine converts in-

structions into one or more

micro-operations (mops). The

mops improve performance

by representing fixed-length,

fixed-field, easy-to-execute

operations. You can individu-

ally schedule the mops, facili-

tating the Pentium II’s out-of-

order execution of in-

structions.

After the decoder creates

mops, it sends them to a 40-

mop-deep reorder buffer

(ROB). The mops then await

dispatch to the execution

portion of the pipeline. The

mops are then either ready for

execution or waiting for data from a memor

y access or a result

from a previous mop. T

o avoid register dependencies, the Pen-

tium II performs renaming: Extra registers represent the x86’s

programmer-visible registers. The dispatch/execute engine

queues ready-for-execution mops within a 20-entr

y, distrib

-

uted-reservation station. The Pentium II determines the data

flow by analyzing which mops depend on each other’

s results.

The processor dispatches mops from anywhere or in any order

within the reser

vation station.

The Pentium II speculatively executes and returns these

mops to the ROB, and the retire engine then evaluates them.

Although the Pentium II executes mops or instructions out of

order

, the device completes the instructions in the original

program order

. Furthermore, speculative execution implies

that the device executes some instructions that never retire.

This situation occurs if the device mispredicts a program

branch. When the Pentium II encounters a mispredicted

branch, it flushes its deep pipelines and removes mops from

the ROB. T

o minimize the possibility of a mispredicted

branch, Intel designers increased the branch target buffer to

512 entries and added histor

y bits to help the prediction algo-

rithm.

The Pentium II, with the same multimedia-extension

instructions as Pentium, comes in a single-edge-contact car

-

tridge with a 512-kbyte L2 cache. This year

, Intel introduced

its Celeron and Pentium II Xeon processors. Celeron, which

comes in a single-edge processor package, is basically a cache

-

less Pentium II and targets the less-than-$1000 PC market. At

the other extreme is Xeon, targeting the midrange to high-

end ser

ver and workstation market. Xeon is a Pentium II with

512 kbytes or 1 Mbyte of L2 cache. It comes in a Slot 2 mod

-

ule—approximately twice the weight and height of a Slot 1

module—and supports four- or eight-way multiprocessing.

Slot 1 processors

Loading...

Loading...