4/17/98 6-91 Addressing Modes and Data Types

Note: For all divides except DIVU.b, the destination register size is the same as indicated by the

instruction (by the “.b”, “.w”, or “.d”) and the source register is half that size.

DIV.w Rd, Rs

(signed 16 bits / 8 bits --> 8 bit quotient, 8 bit remainder)

Bytes: 2

Clocks: 14

Operation: (RdL) <-- 8-bit integer portion of (Rd) / (Rs) (signed divide)

(RdH) <-- 8-bit remainder of (Rd) / (Rs)

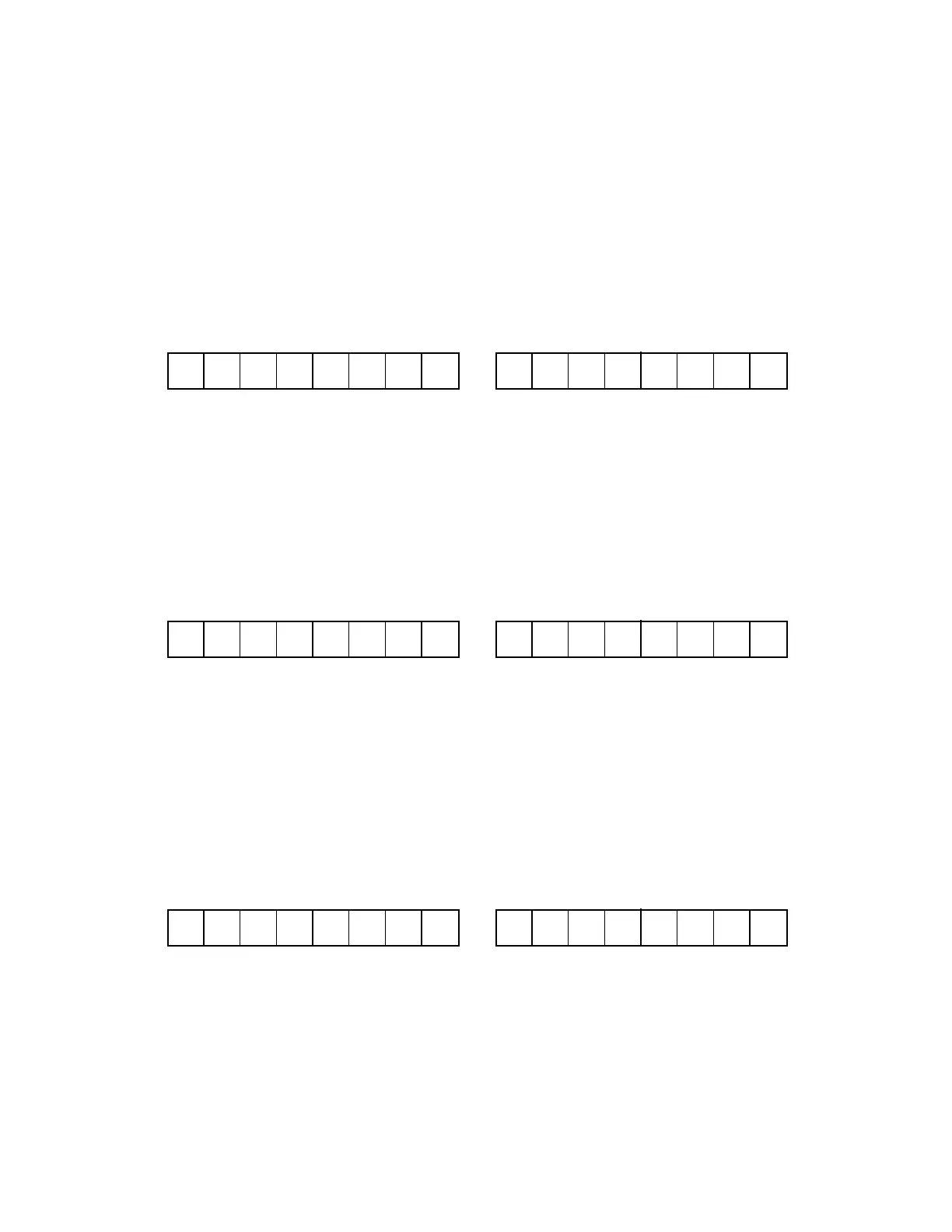

Encoding:

DIV.w Rd, #data8

(signed 16 bits / 8 bits --> 8 bit quotient, 8 bit remainder)

Bytes: 3

Clocks: 14

Operation: (RdL) <-- 8-bit integer portion of (Rd) / #data8 (signed divide)

(RdH) <-- 8-bit remainder of (Rd) / #data8

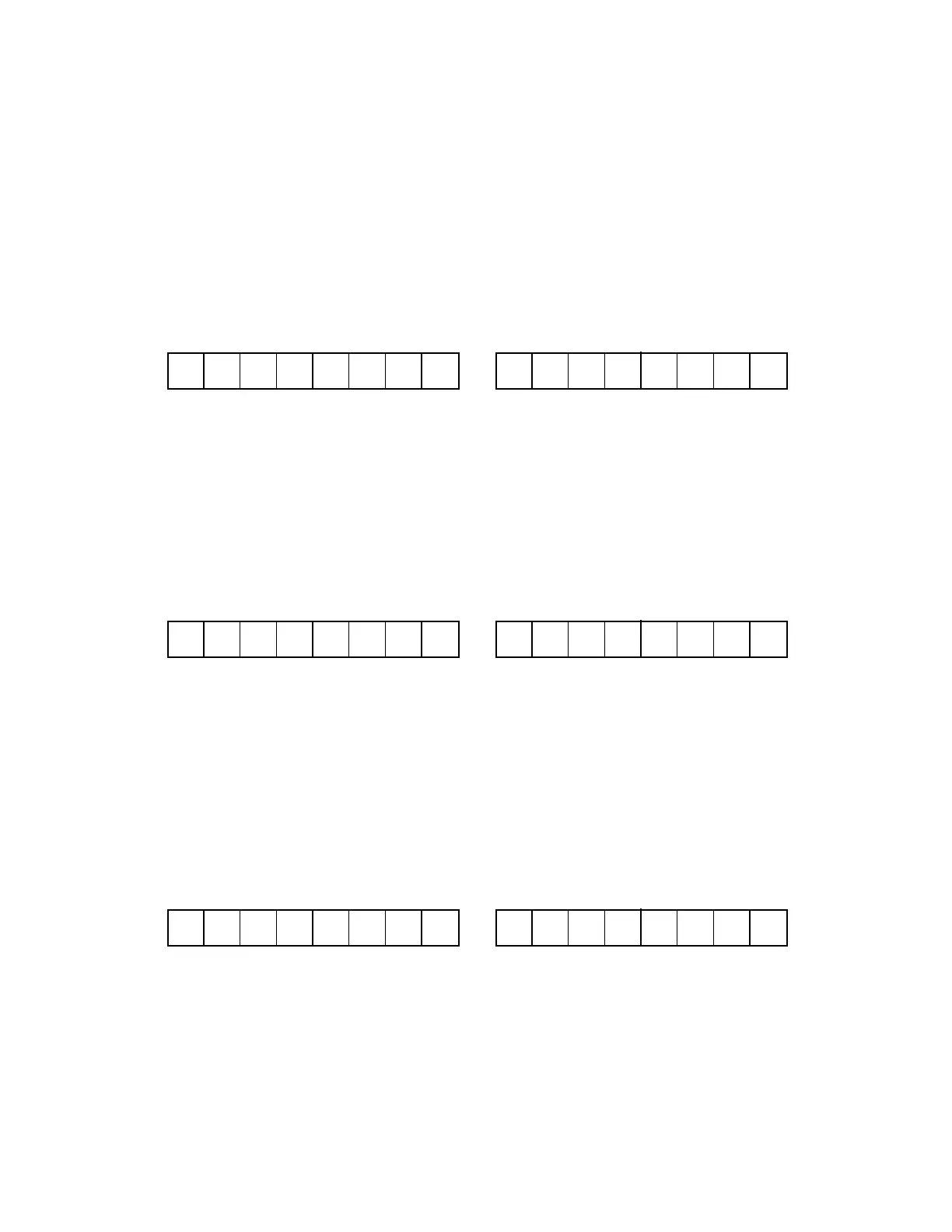

Encoding:

byte 3: #data8

DIV.d Rd, Rs

(signed 32 bits / 16 bits --> 16 bit quotient, 16 bit remainder)

Bytes: 2

Clocks: 24

Operation: (Rd) <-- 16-bit integer portion of (Rd) / (Rs) (signed divide)

(Rd+1)<-- 16-bit remainder of (Rd) / (Rs)

Encoding:

1 1 1 0 0 1 1 1 d d d d s s s s

1 1 1 0 1 0 0 0 d d d d 1 0 1 1

1 1 1 0 1 1 1 1 d d d 0 s s s s

Loading...

Loading...