XA User Guide 6-92 4/17/98

DIV.d Rd, #data16

(signed 32 bits / 16 bits --> 16 bit quotient, 16 bit remainder)

Bytes: 4

Clocks: 24

Operation: (Rd) <-- 16-bit integer portion of (Rd) / #data16 (signed divide)

(Rd+1)<-- 16-bit remainder of (Rd) / #data16

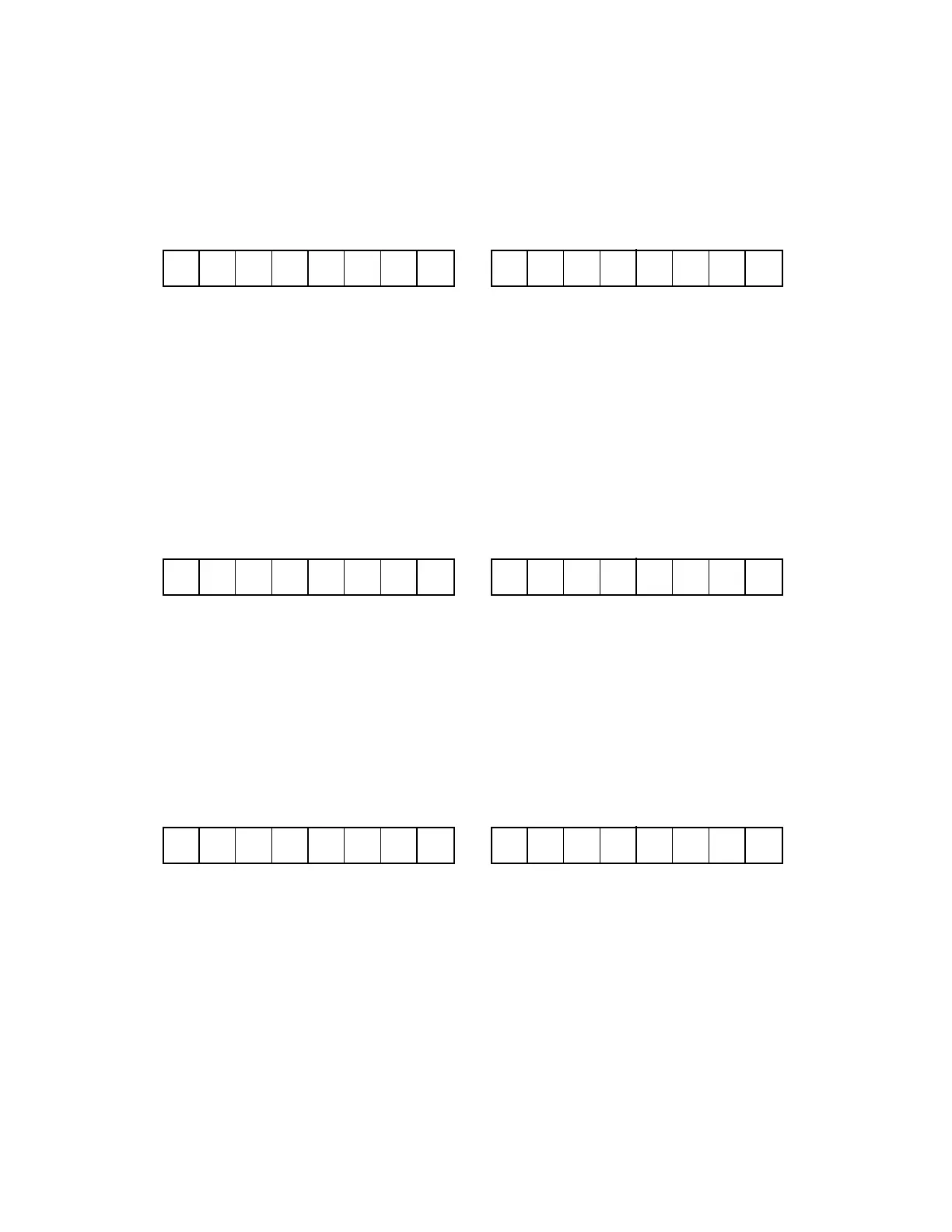

Encoding:

byte 3: upper 8 bits of #data16

byte 4: lower 8 bits of #data16

DIVU.b Rd, Rs

(unsigned 8 bits / 8 bits --> 8 bit quotient, 8 bit remainder)

Bytes: 2

Clocks: 12

Operation: (RdL) <-- 8-bit integer portion of (RdL) / (Rs) (unsigned divide)

(RdH) <-- 8-bit remainder of (RdL) / (Rs)

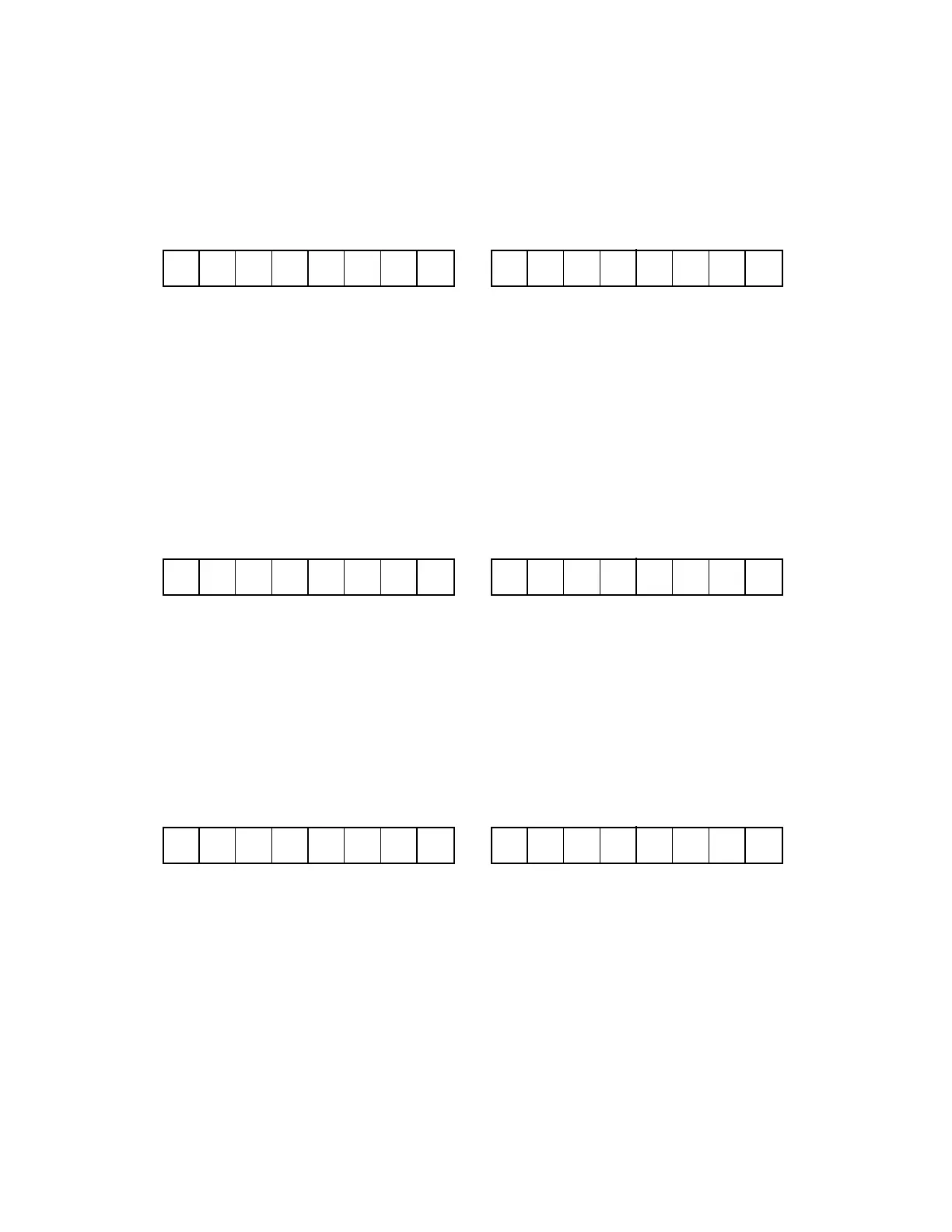

Encoding:

DIVU.b Rd, #data8

(unsigned 8 bits / 8 bits --> 8 bit quotient, 8 bit remainder)

Bytes: 3

Clocks: 12

Operation: (RdL) <-- 8-bit integer portion of (RdL) / #data8 (unsigned divide)

(RdH) <-- 8-bit remainder of (RdL) / #data8

Encoding:

byte 3: #data8

1 1 1 0 1 0 0 1 d d d 0 1 0 0 1

1 1 1 0 0 0 0 1 d d d d s s s s

1 1 1 0 1 0 0 0 d d d d 0 0 0 1

Loading...

Loading...