XA User Guide 7-10 4/17/98

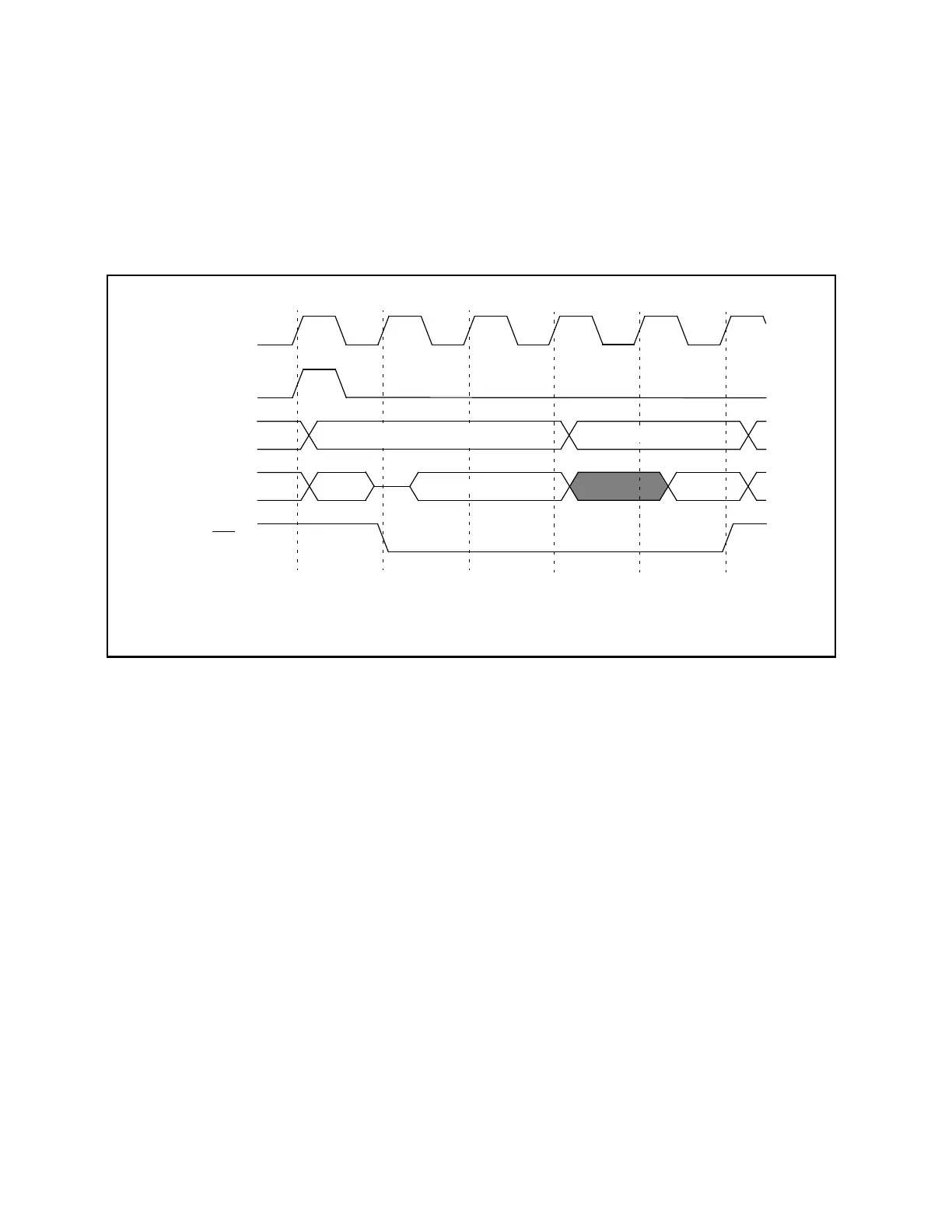

Word Read on an 8-Bit Data Bus

When the XA external bus is configured for an 8-bit data width, a word read operation is

automatically performed as two byte reads at sequential addresses. Since the XA CPU requires

word operations to be performed at even addresses, the second half of any word read on a byte-

wide bus always uses the same upper address latched by ALE. for this operation, the low order

byte first is read at the even byte address, then the high order byte is read at the next (odd)

address. So, only one ALE is required in this case. The diagram below shows this sequence.

Figure 7.9 Word Read on 8-Bit Data Bus

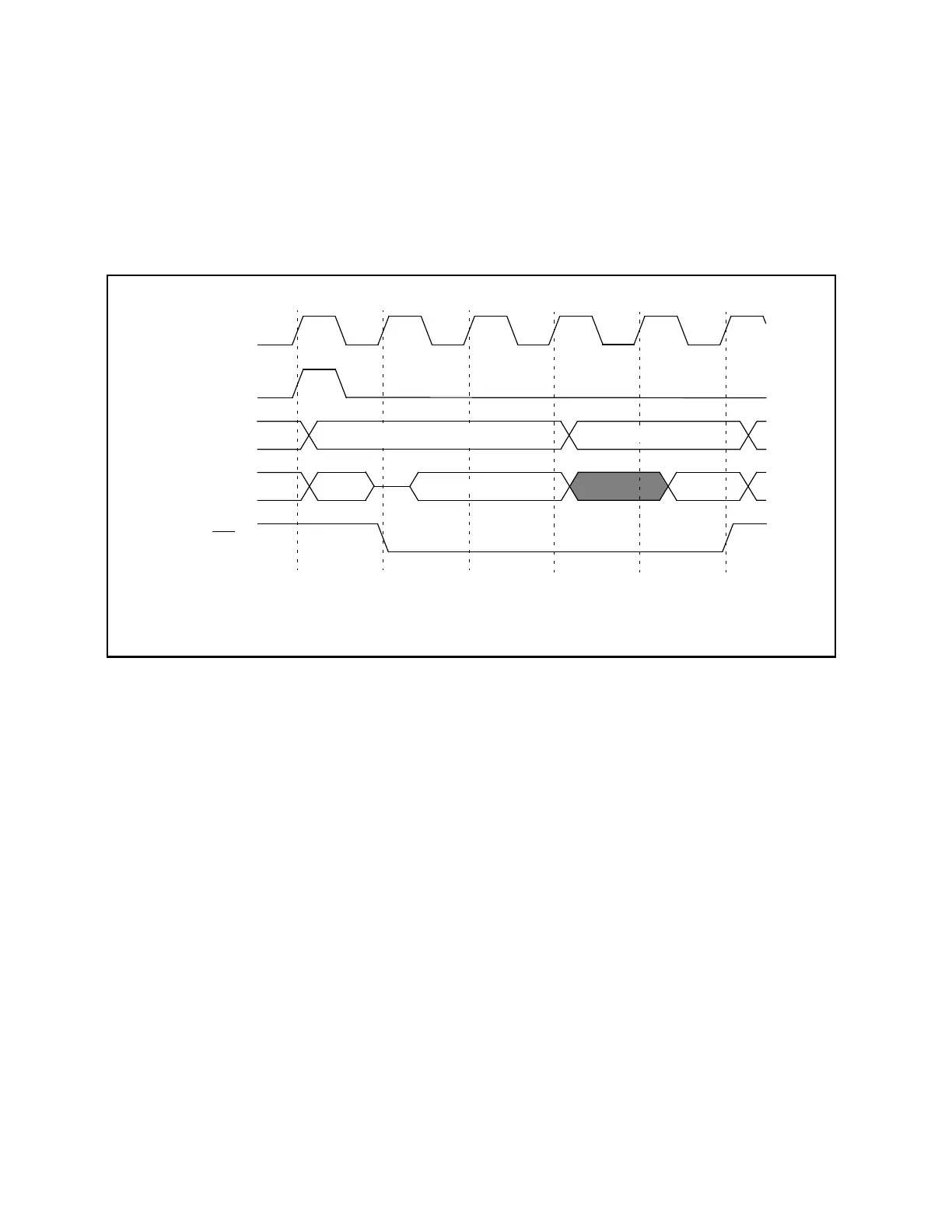

Byte Read on a 16-Bit Data Bus

When an instruction causes a read of one byte of data from the external bus, when it is

configured for 16-bit width, a simple read operation is performed. This results in 16 bits of data

being received by the XA, which uses only the byte that was requested by the program. There is

no way to distinguish a byte read from a word read on the external bus when it is configured for

a 16-bit width.

Address/

Data bus

RD

Address bus

ALE

address

data in to XA

XTAL1

data in

even address odd address

Note: the timing of this type of bus operation is user programmable. The timing shown

here is generated by the Bus Timing Register setup: ALEW = 0, DRA1/0 = 01, DR1/0 = 01.

to XA

Loading...

Loading...