XA User Guide 7-12 4/17/98

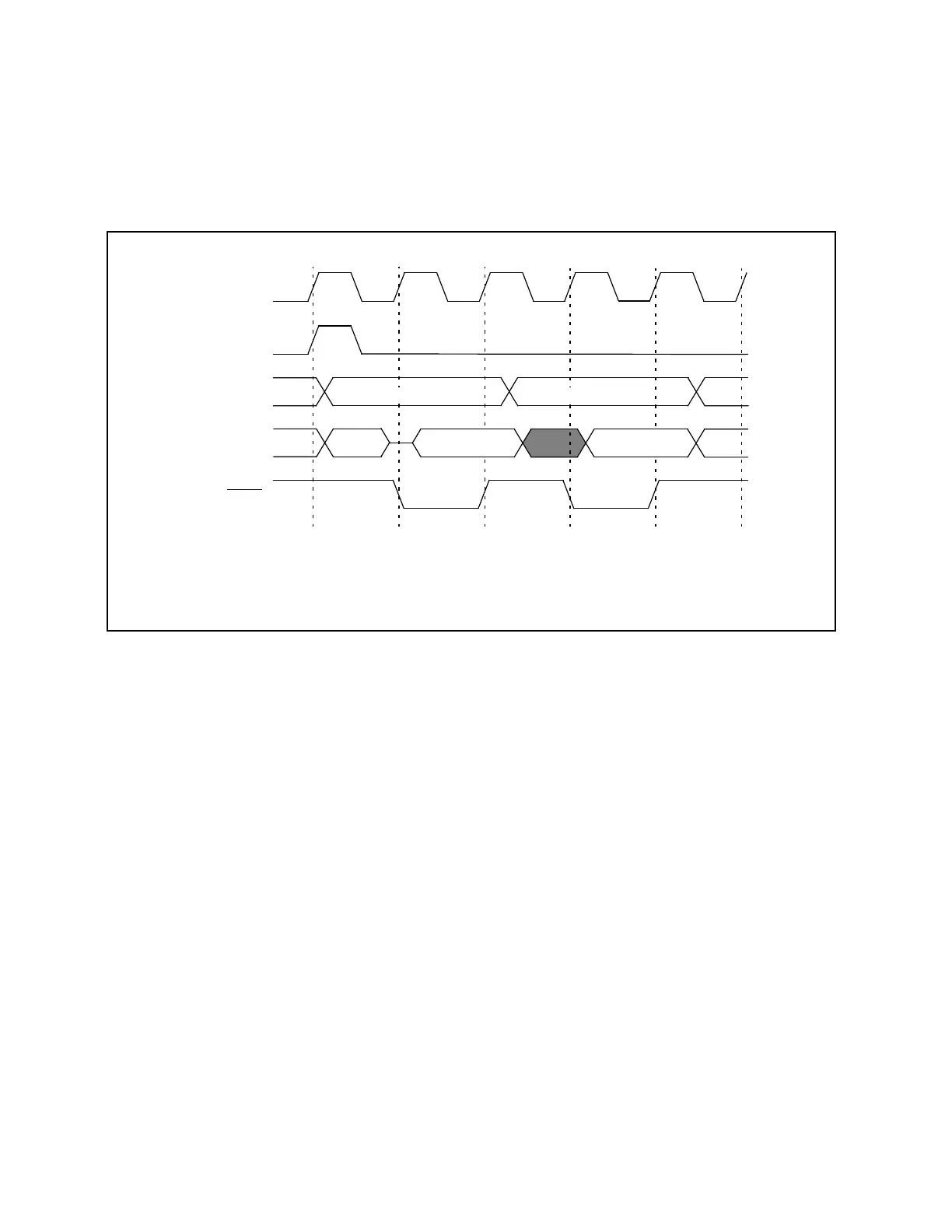

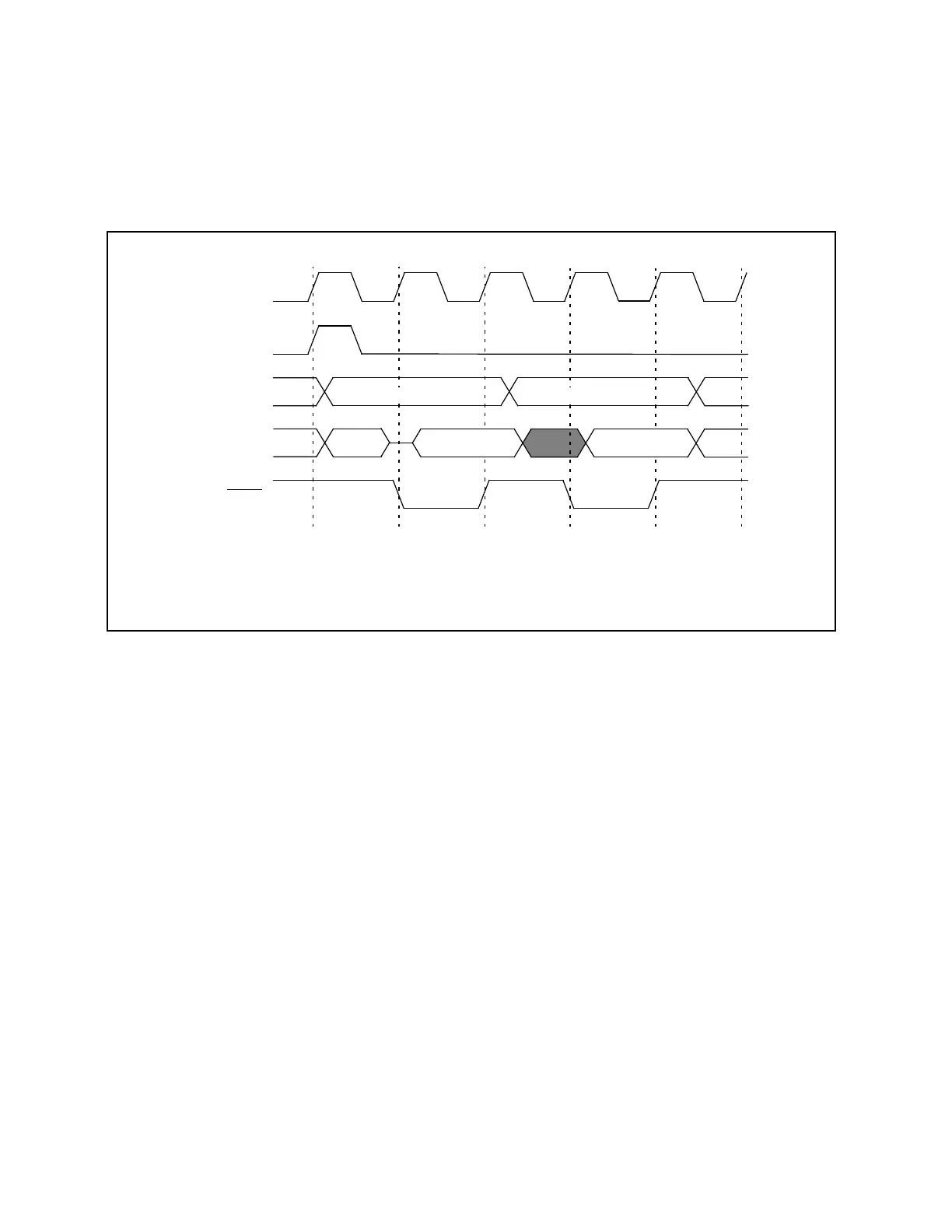

Word Write on an 8-Bit Data Bus

When a word write operation is done with the bus configured to an 8-bit width, the XA

automatically performs two byte writes. First, the low order byte is written (at the even byte

address), then the high order byte is written at the next (odd) address. As with a word read on an

8-bit bus, this requires only a single ALE cycle at the beginning of the process. This sequence is

shown in the following diagram.

Figure 7.11 Word Write on 8-Bit Data Bus

Address/

Data bus

WRL

Address bus

ALE

address

data out

from XA

XTAL1

data out

from XA

even address odd address

Note: the timing of this type of bus operation is user programmable. The timing shown here

is generated by the Bus Timing Register setup: ALEW = 0, DWA1/0 = 00, DW1/0 = 00,

WM0 = 0, WM1 = 0.

Loading...

Loading...