80C32/80C52

Rev. G (14 Jan. 97)

16

MATRA MHS

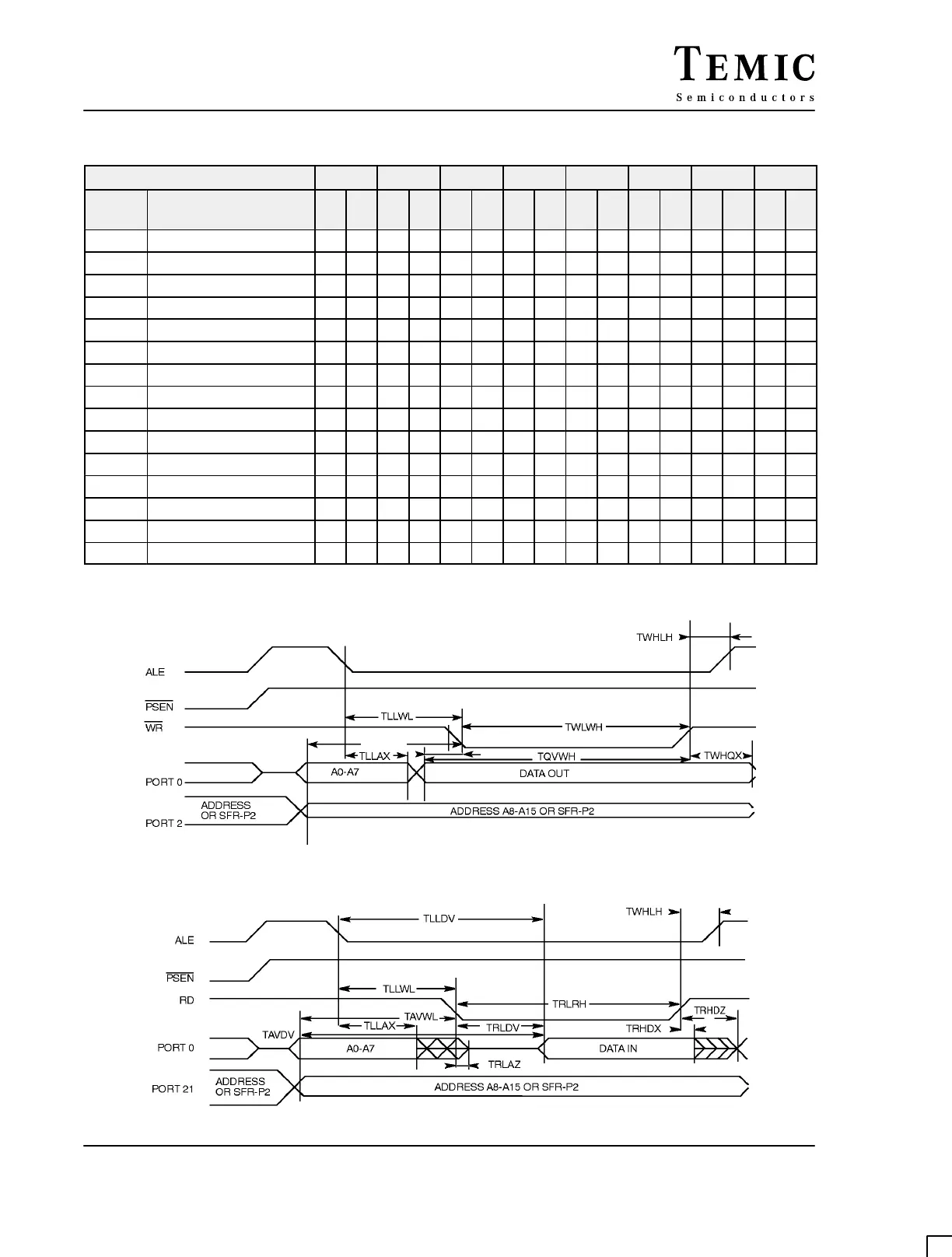

External Data Memory Characteristics (values in ns)

16 MHz 20 MHz 25 MHz 30 MHz 36 MHz 40 MHz 42 MHz 44 MHz

SYM-

BOL

PARAMETER min max min max min max min max min max min max min max min max

TRLRH RD pulse Width 340 270 210 180 120 100 90 80

TWLWH WR pulse Width 340 270 210 180 120 100 90 80

TLLAX Address Hold After ALE 85 85 70 55 35 30 25 25

TRLDV RD to Valid Data in 240 210 175 135 110 90 80 70

TRHDX Data hold after RD 0 0 0 0 0 0 0 0

TRHDZ Data float after RD 90 90 80 70 50 45 40 35

TLLDV ALE to Valid Data In 435 370 290 235 170 150 140 130

TAVDV Address to Valid Data IN 480 400 320 260 190 180 175 170

TLLWL ALE to WR or RD 150 250 135 170 120 130 90 115 70 100 60 95 55 90 50 85

TAVWL Address to WR or RD 180 180 140 115 75 65 60 55

TQVWX Data valid to WR transition 35 35 30 20 15 10 8 6

TQVWH Data Setup to WR transition 380 325 250 215 170 160 150 140

TWHQX Data Hold after WR 40 35 30 20 15 10 8 6

TRLAZ RD low to Address Float 0 0 0 0 0 0 0 0

TWHLH RD or WR high to ALE high 35 90 35 60 25 45 20 40 20 40 15 35 13 33 13 33

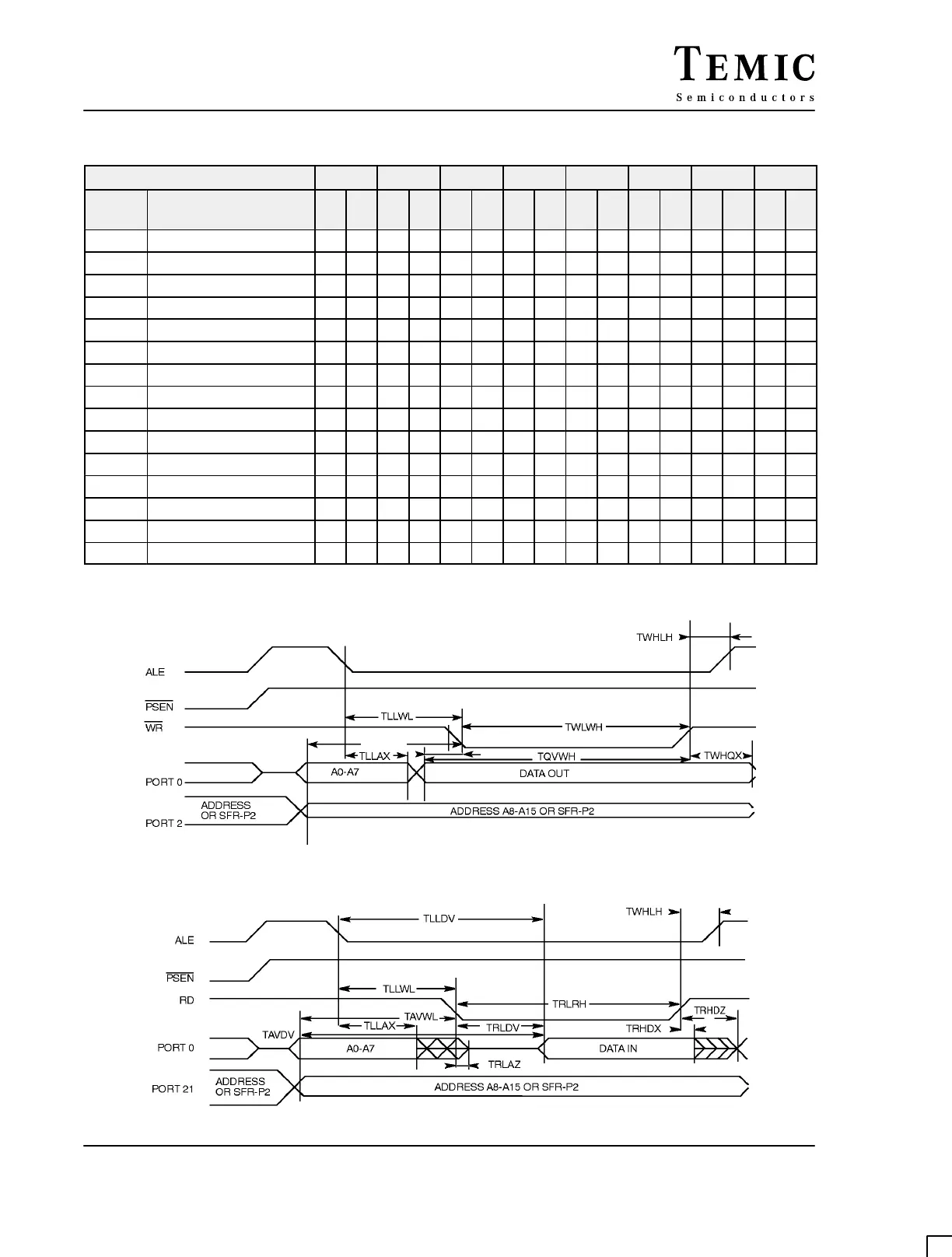

External Data Memory Write Cycle

TAVWL

TQVWX

External Data Memory Read Cycle

Loading...

Loading...