21

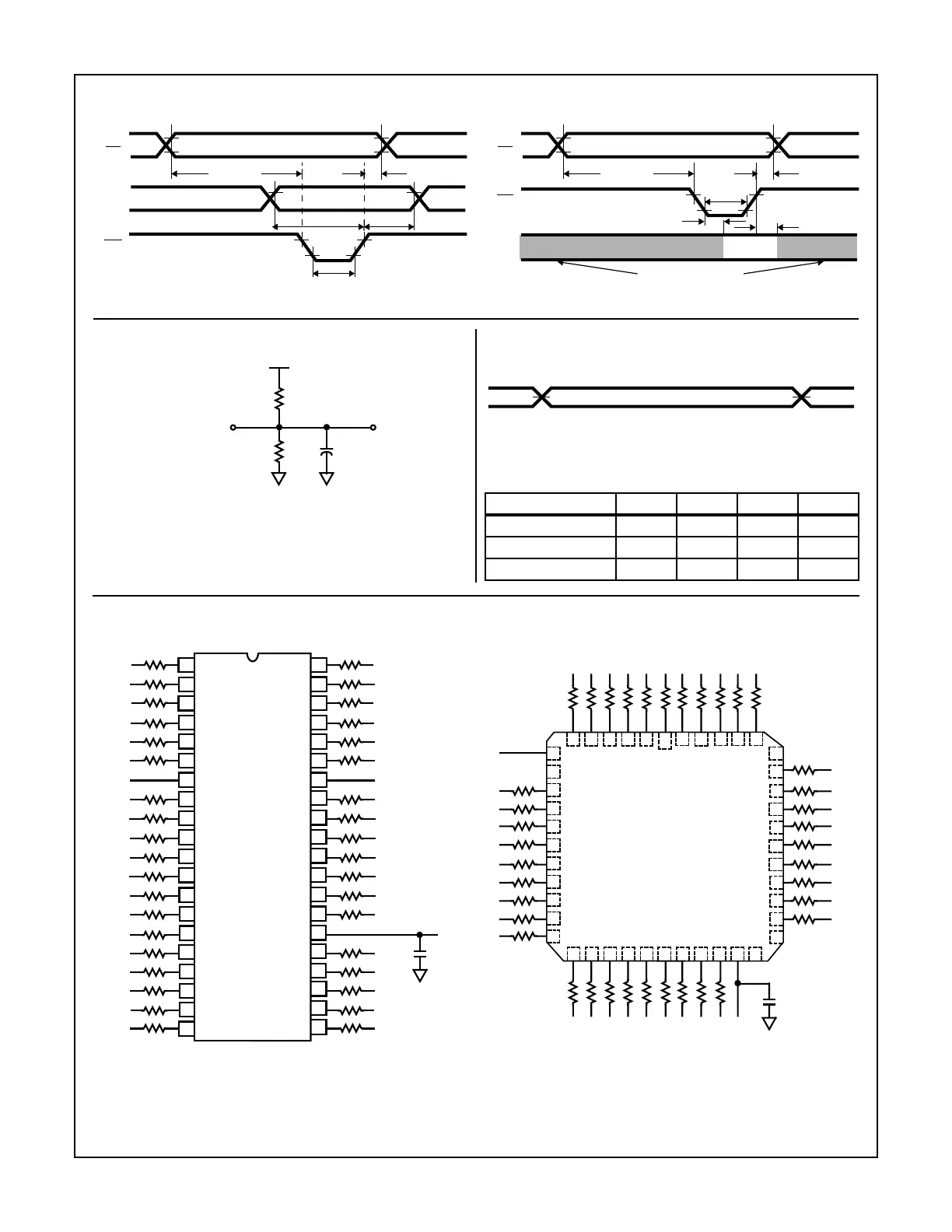

AC Test Circuit AC Testing Input, Output Waveforms

Burn-In Circuits

FIGURE 30. WRITE TIMING FIGURE 31. READ TIMING

Timing Waveforms

(Continued)

WR

DATA

A0-A1,

CS

BUS

tWW (9)

tDW (10) tWD (11)

tWA (8)

tAW (7)

RD

DATA

A0-A1,

CS

BUS

tRR (3)

tRA (2)

tAR (1)

VALID

(4) tRD

tDF (5)

HIGH IMPEDANCE

R1

V1

OUTPUT FROM

DEVICE UNDER

TEST

NOTE: Includes STRAY and JIG Capacitance

TEST

POINT

C1

R2

(SEE NOTE)

TEST CONDITION DEFINITION TABLE

TEST CONDITION V1 R1 R2 C1

1 1.7V 523Ω Open 150pF

2V

CC

2kΩ 1.7kΩ 50pF

3 1.5V 750Ω Open 50pF

INPUT

VIH + 0.4V

VIL - 0.4V

1.5V 1.5V

VOH

VOL

OUTPUT

AC Testing: All AC Parameters tested as per test circuits. Input RISE and

FALL times are driven at 1ns/V.

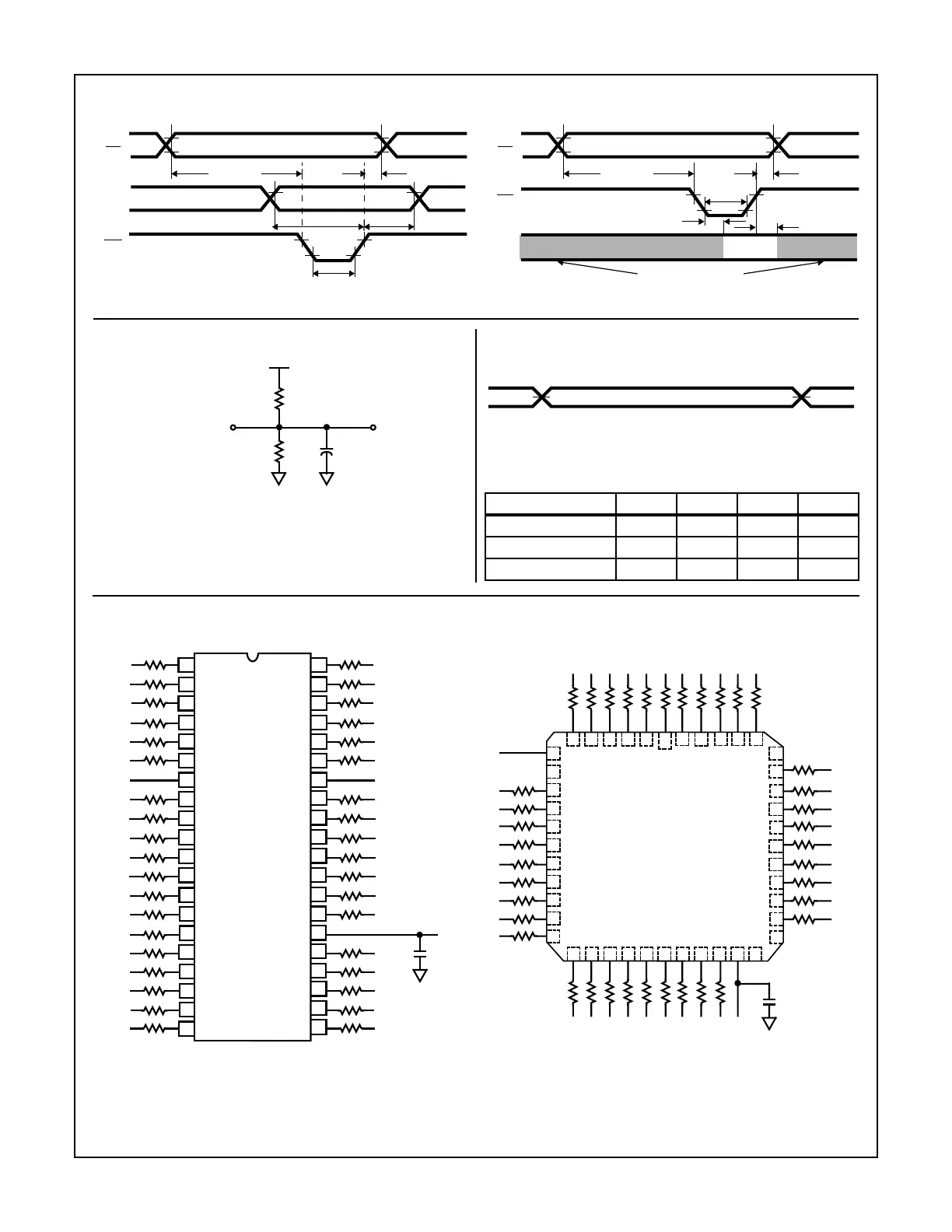

MD82C55A CERDIP

NOTES:

1. V

CC

= 5.5V ± 0.5V

2. VIH = 4.5V ± 10%

3. VIL = -0.2V to 0.4V

4. GND = 0V

MR82C55A CLCC

NOTES:

1. C1 = 0.01µF minimum

2. All resistors are 47kΩ± 5%

3. f0 = 100kHz ± 10%

4. f1 = f0 ÷ 2; f2 = f1 ÷ 2; . . . ; f15 = f14 ÷ 2

F7

F8

F9

F4

F3

GND

F0

F1

F10

F6

F7

F8

F9

F6

F7

F8

F9

F10

F6

33

34

35

36

37

38

40

32

31

30

29

24

25

26

27

28

21

22

23

13

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

39

1

F12

F13

F14

F2

F5

F15

F11

F12

F13

F14

F15

F11

F12

V

CC

F13

F14

F15

F11

F12

F11

C1

F10

V

CC

F13

F14

F10

F9

F8

F7

F12

F11

F15

GND

F0

F10

F6

F7

F8

F9

F10

F6

F1

14

13

12

11

10

9

8

7

17

16

15

25

30

35

39

38

37

36

33

34

32

31

29

4

6 3

1

40414243

44

2827262524232221201918

F3

F4

F9

F8

F12

F13

F14

F2

F5

F15

F12

F13

F14

F15

F11

F12

F11

F11

F6

F7

C1

82C55A

Loading...

Loading...