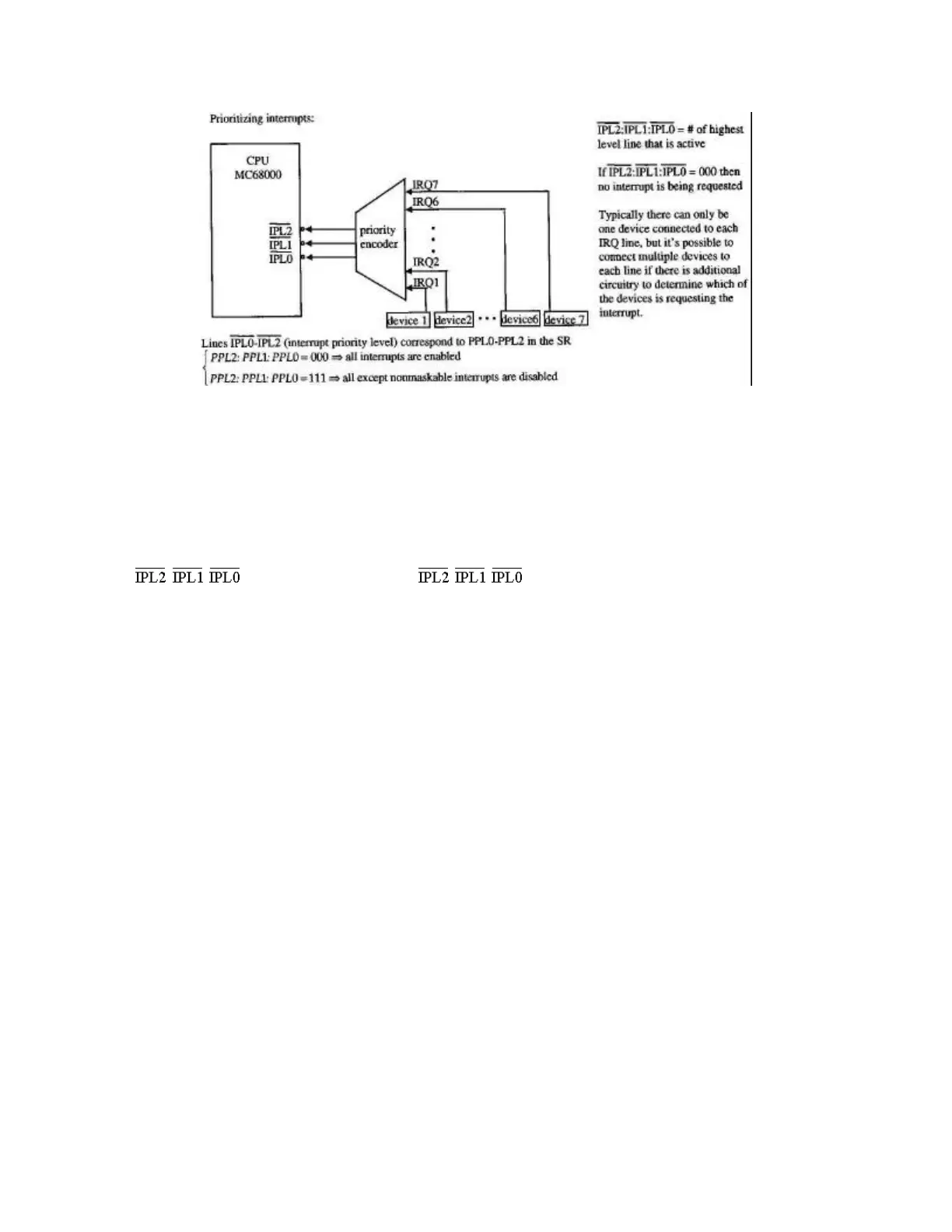

Motorola Interrupt Priority Encoder (from Orejel)

There is one exception to this. An interrupt with priority level 7 is a non-maskable interrupt

(NMI). Just as for Intel processors, NMIs are typically reserved for only a few situations,

generally entailing such catastrophic events as power failure and hardware error. Unlike Intel

NMIs, it is impossible to disable an NMI on this chip. Thus, even if the PPL bits are set to seven,

the CPU will always recognize a level 7 interrupt. We can express this relationship with the

following pseudo-code:

if ( : : PPL2:PPL1:PPL0) or ( : : = 7)

process interrupt

else ignore any pending interrupt request

On the Motorola chip, once the CPU recognizes an interrupt request, it must set the interrupt

mask to the same level as the interrupt it is processing. Until the CPU can send a signal to the

device that is generating the interrupt to let it know that it is receiving the attention it is

requesting, it continues to assert the interrupt request. The CPU would accept the interrupt,

complete the actions for the exception processing state, then would detect the (same) interrupt

request. Since the priority level for the device is (still) higher than the processor priority level,

the CPU would again accept the interrupt. Obviously, this process would continue until there

was a supervisor stack overflow and the device would never receive service. To put it more

simply, the continuing interrupt request signal causes the device to "interrupt itself". The Intel

8259A controller solved this problem with the ISR. Since the Motorola machines have a priority

encoder, rather than a controller, the ISR register does not exist. If the Motorola CPU did not

reset the PPL bits, the requesting device would continue to request an interrupt. Setting the PPL

bits to the same level as the interrupt that the CPU is accepting means that the device's priorty

level is no longer high enough to merit a response from the CPU. This in turn allows the CPU to

service the device's request without further interruptions (unless a higher-priority device requests

an interrupt at this moment).

This scheme presents a problem in terms of NMIs, both for Intel and Motorola processors, since

it is impossible to set priority high enough to ignore them. For this reason, NMIs are edge-

sensitive or edge-triggered. This means that the CPU recognizes them only at a specific moment

in relationship to the signals that the system clock generates. This clock emits signal pulses,

alternating between high and low voltages at regular intervals. These transitions can be seen as

Loading...

Loading...