CertusPro-NX SerDes/PCS Usage Guide

Preliminary Technical Note

34 © 2020-2021 Lattice Semiconductor FPGA-TN-02245-0.81

All rights reserved. CONFIDENTIAL

which can be enabled to properly lock the CDR and reach a valid

state of receiver adaptation.

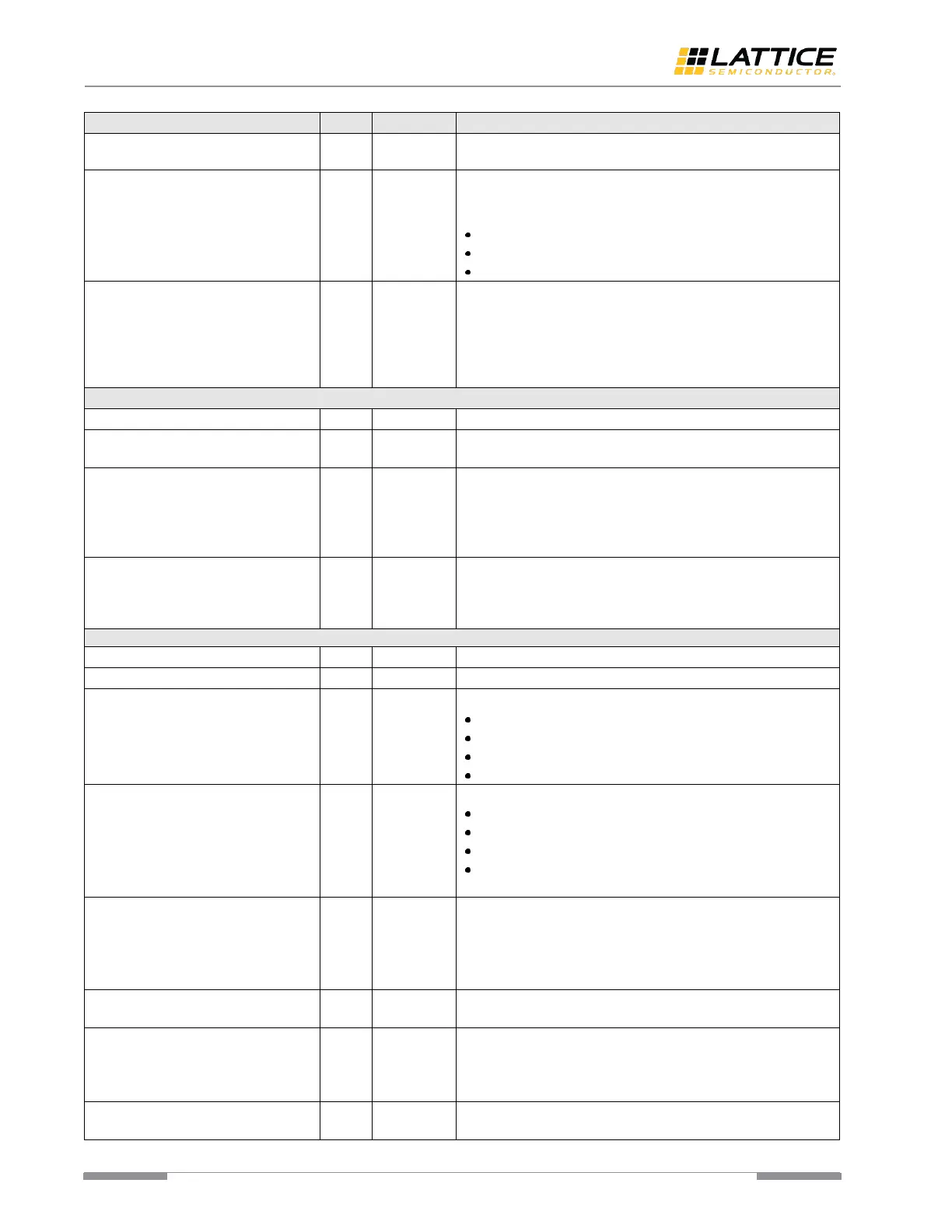

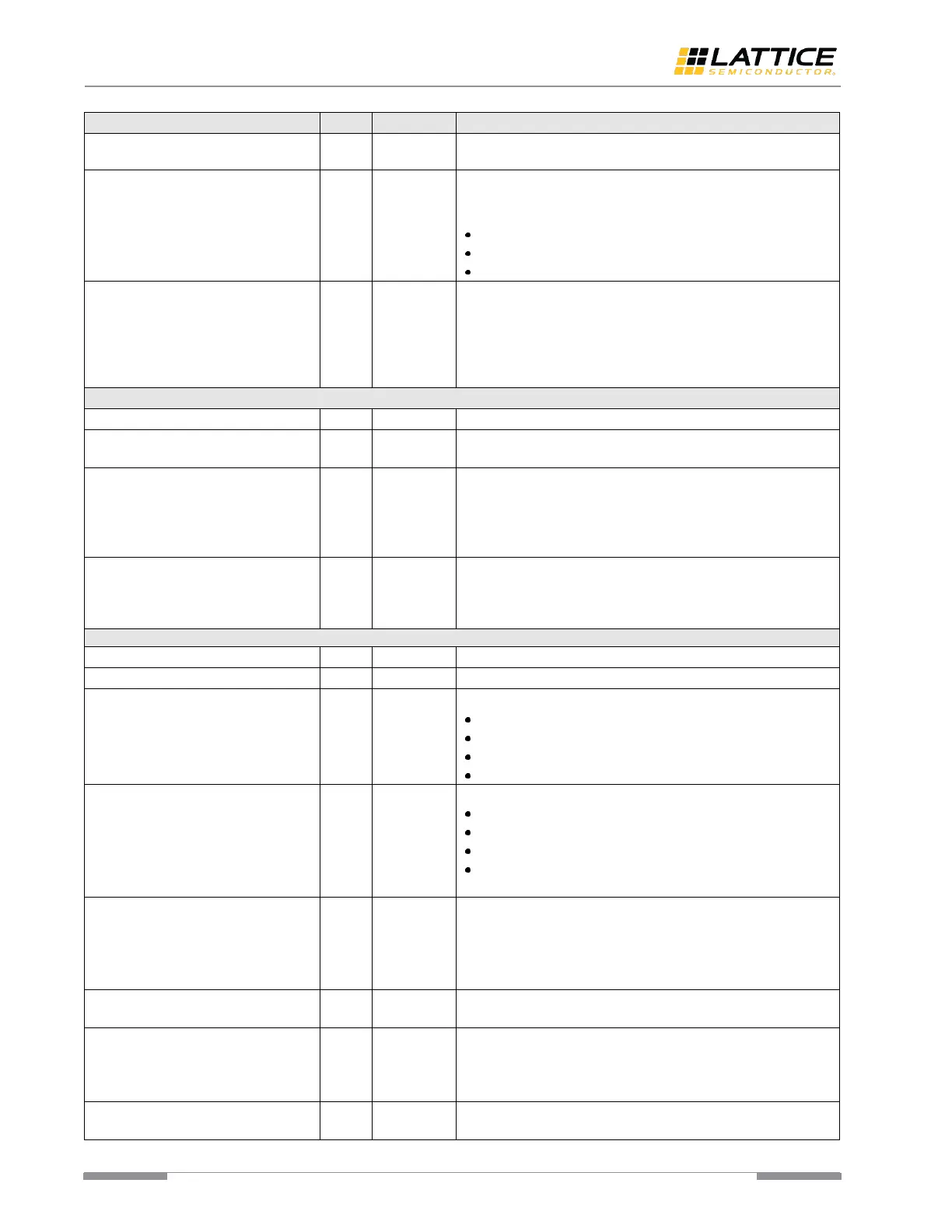

Rx equalization link evaluation change. This signal is a per-lane

signal which is used by the PHY layer to indicate what the next

direction of coefficient change should be:

[5:4]: C+1(01b incr/00b: same/10b decr)

[3:2]: C0 (01b incr/00b: same /10b decr)

[1:0]: C-1 (01b incr/00b: same/10b decr)

Rx Equalization Link Evaluation FOM. This signal is a per-lane

signal which is used by the PHY layer to indicate what FOM at

the end of an evaluation is.

The higher this value, the better equalization result. A low FOM

is not a direct indicator of a high bit error ratio, and may vary

based on the loss of the channel.

PIPE CLKREQ# and L1 Substance Signals

L1 substate request. Active low request to enter L1 substate.

L1 substate acknowledge. Active low acknowledge to enter L1

substate.

pipe_rxelecidle_disable_i

L1 substate disable activity detector. Through this signal, the

MAC effectively disable the activity detector circuit (power

down), and move the PHY to either L1.1 (Tx Common Mode

voltage is still valid) or L1.2 (Tx Common Mode voltage is

disabled).

pipe_txcommonmode_disable_i

L1 substate disabled Tx Common Mode voltage. Through this

signal, the MAC effectively configure the Tx driver into Hi-Z

(power down) and move the PHY to either L1.2 (Tx Common

Mode voltage is disabled).

Register control to reset lane3 in PCIE mode for link1.

Register control to reset lane0~3 in PCIE mode for link0.

PHY Power Down control.

2’b00 – P0 (normal operation)

2’b01 – P0s (Tx L0s)

2’b10 – P1 (L1 or Reset)

2’b11 – P2 (L2)

PHY rate control.

2’b11 – 16G

2’b10 – 8G

2’b01 – 5G

2’b00 – 2.5G

Must be set to speed supported by the core.

pipe_tx_detect_rx_loopback_LL_i

If pipe_power_down_LL_i == 2’10, 1’b1 – PHY Tx Detection

Request.

If pipe_tx_elec_idle_LL_i == 1’b0, 1’b1 – PHY Rx to Tx Loopback

Request.

Otherwise, 1’b0.

Set and hold this signal to 1’b1 to request the PHY to evaluate

the far end transmitter Tx Eq settings

pipe_invalid_request_LL_i

Rx equalization invalid request.

When this signal is asserted, the PHY stops the current

evaluation and provides a new direction through

pipe_linkevalchange_o signal.

Rx equalization preset hint.

Used to indicate the PHY what seems to be a good starting point

Loading...

Loading...