207

_____________________________________________________________________________________________

10.6 GP-IB Command Transfer Methods

______________________________________________________________________________________________

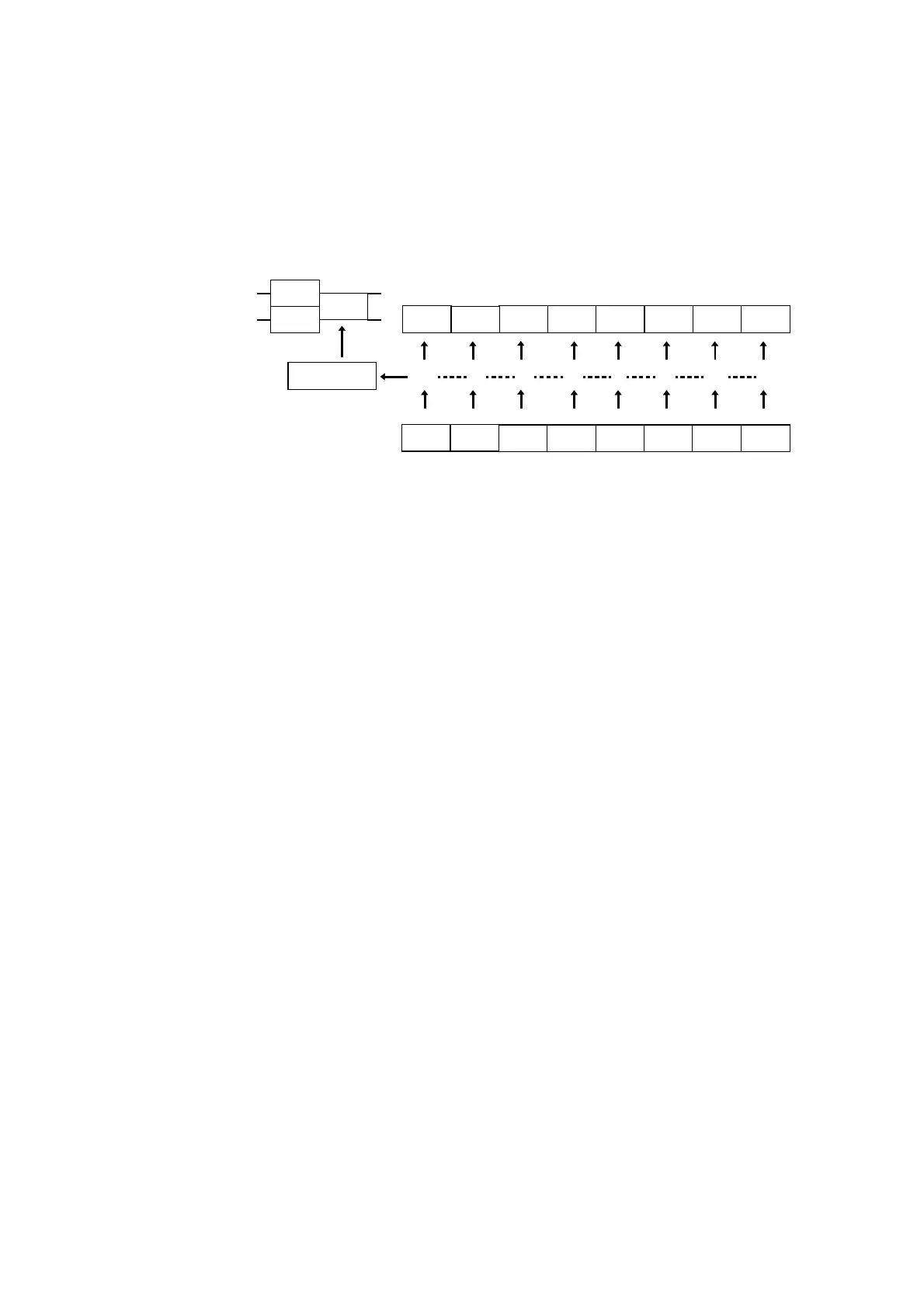

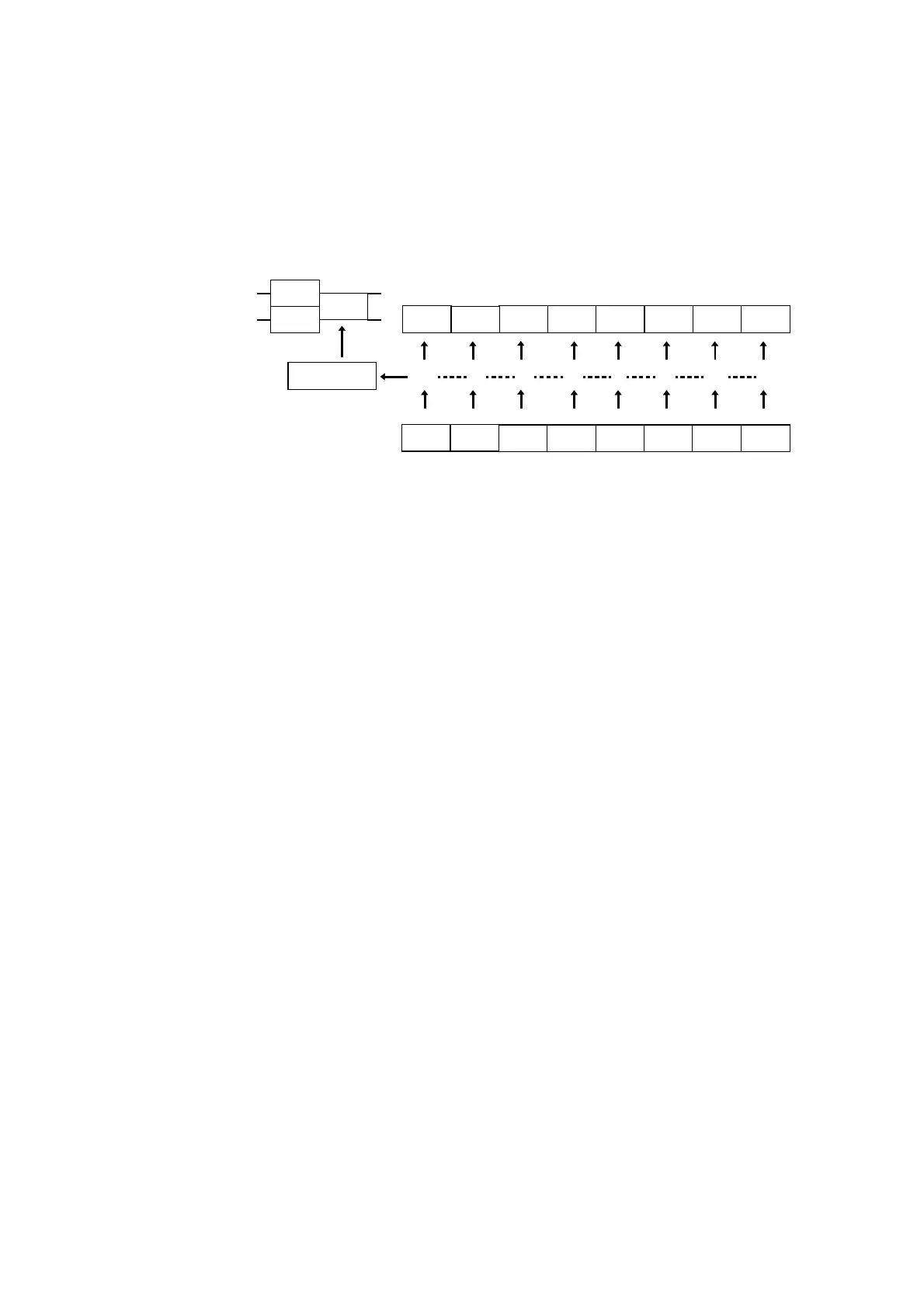

CME EXE

Logical sum

CME EXE

PON URQ

DDE QYE RQC OPC

DDE QYE RQC OPCPON

URQ

ESB

RQS

MSS

bit 6

bit 5

Standard event status register (SESR)

Standard event status enable register (SESER)

S

tatus byte register (STB)

bit 7

bit 6

bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

bit 3 bit 2 bit 1 bit 0bit 5 bit 4bit 7 bit 6

Event Registers

(1) Standard event status register (SESR)

The standard event status register is an 8-bit register. If any bit in the

standard event status register is set to 1 (after masking by the standard event

status enable register), bit 5 (ESB) of the status byte register is set to 1.

The standard event status register is cleared in the following four situations:

①

When a ∗

CLS

command is received.

②

When an ∗

ESR?

query is received.

③

When the unit is powered on.

④

When the I/F is Switched.

Loading...

Loading...