209

_____________________________________________________________________________________________

10.6 GP-IB Command Transfer Methods

______________________________________________________________________________________________

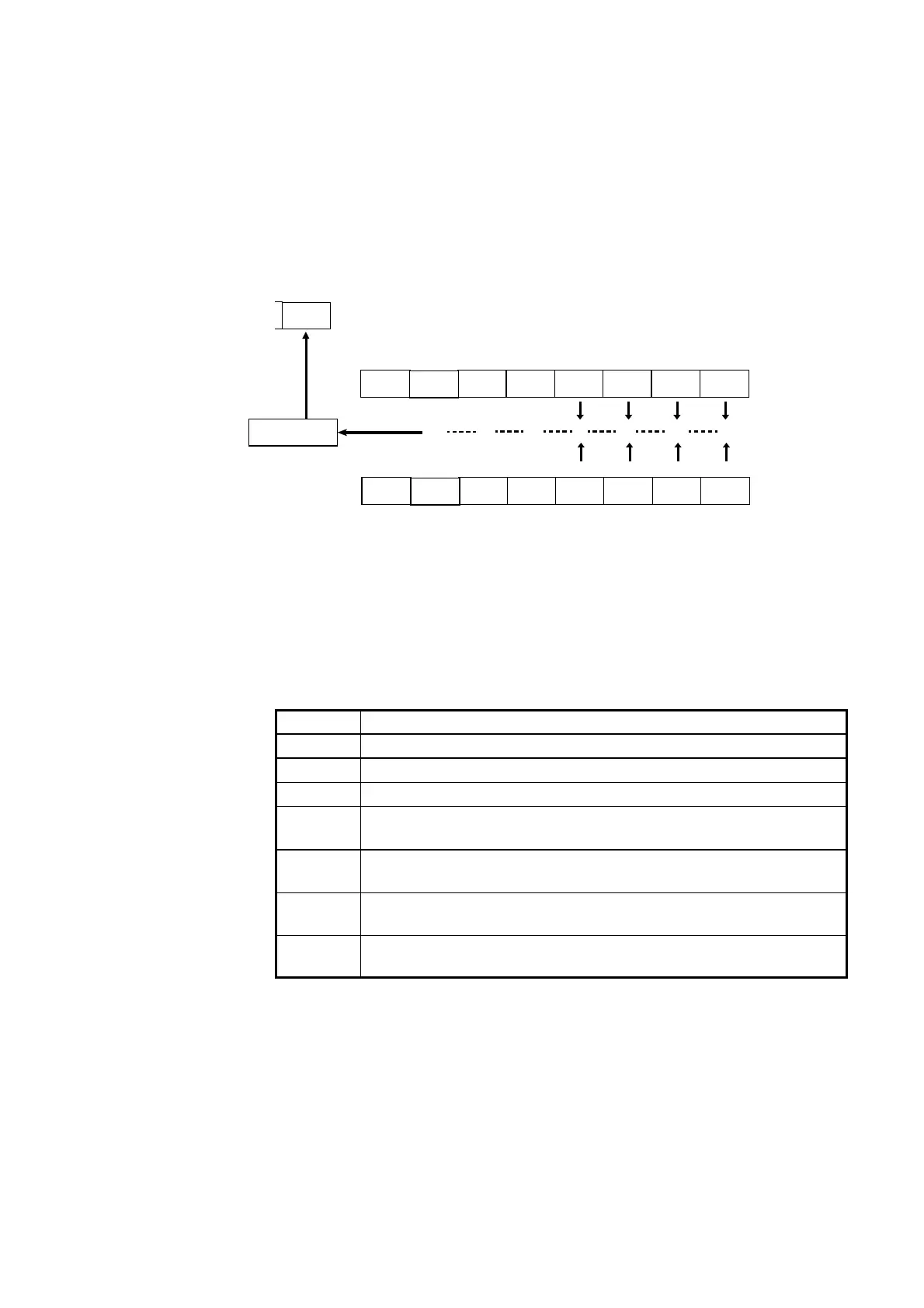

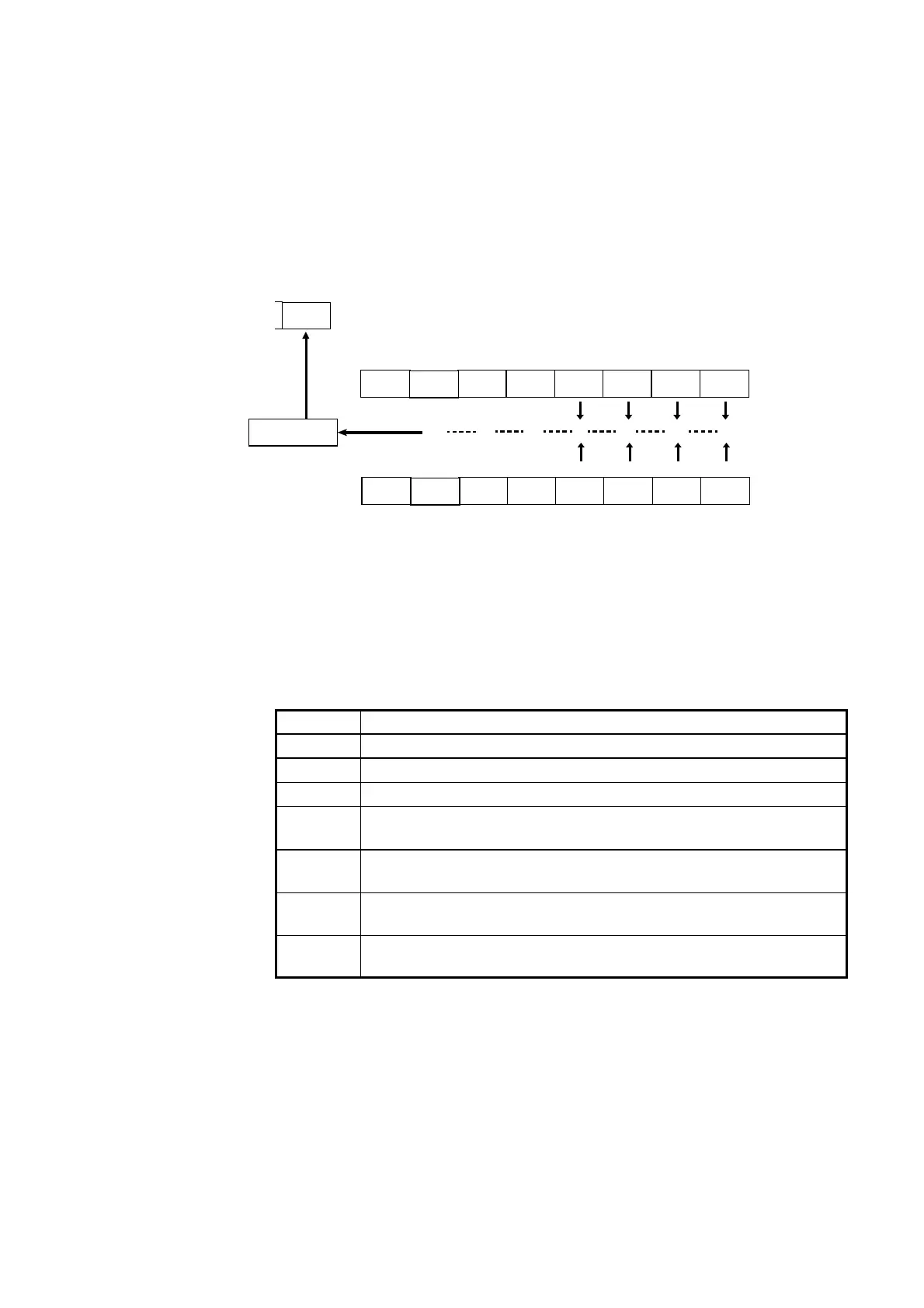

UnusedUnused EOM LFAIL UFAIL PASSUnused

Unused

UnusedUnused EOM LFAIL UFAIL PASSUnused

Unused

bit 0

ESB0

Event status register 0 (ESR0)

Event status enable register 0 (ESER0)

Logical sum

Status byte register (STB)

bit 7

bit 6

bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

bit 7

bit 6

bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

Bit 7 Unused

Bit 6 Unused

Bit 5 Unused

Bit 4 Unused

Bit 3

EOM

Test completed

Bit 2

LFAIL

Below lower-limit of comparator

Bit 1

UFAIL

Above upper-limit of comparator

Bit 0

PASS

Within limits of comparator

(3) Event status register 0 (ESR0)

An 8-bit event status register is provided for managing events on the 3153.

If any bit in this event status register is set to 1 (after masking by the

corresponding event status enable register), the following happens:

For event status register 0, bit 0 of the status byte register (ESB0) is set to 1.

Event status register 0 is cleared in the following three situations:

①

When a

∗CLS command is received.

②

When an

:ESR0?

query is received.

③

When the unit is powered on.

Event status register 0 (ESR0) bit assignments

Loading...

Loading...