TMS320C6455

SPRS276M –MAY 2005–REVISED MARCH 2012

www.ti.com

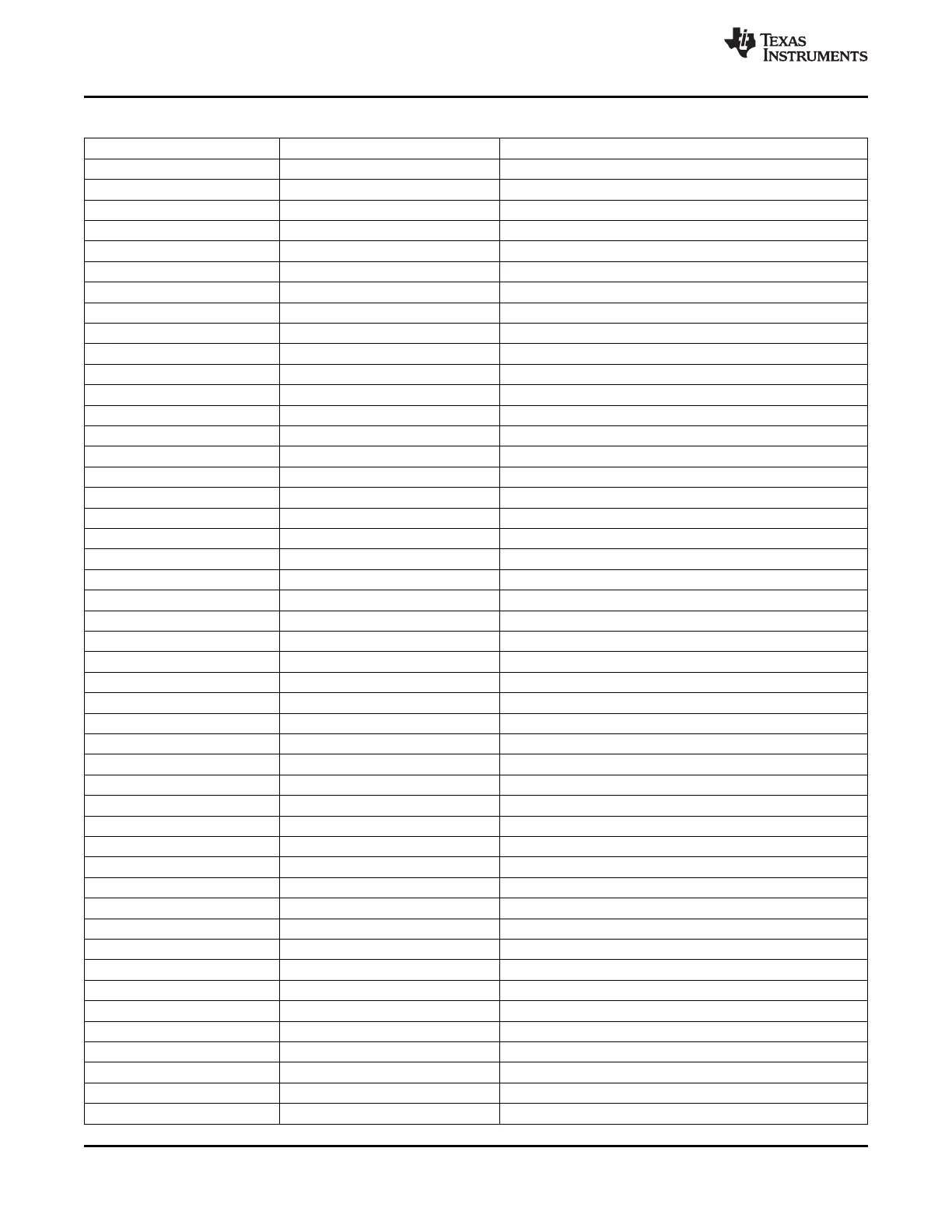

Table 7-112. RapidIO Control Registers (continued)

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02D0 0884 RIO_RXU_MAP_H16 Mailbox-to-Queue Mapping Register H16

02D0 0888 RIO_RXU_MAP_L17 Mailbox-to-Queue Mapping Register L17

02D0 088C RIO_RXU_MAP_H17 Mailbox-to-Queue Mapping Register H17

02D0 0890 RIO_RXU_MAP_L18 Mailbox-to-Queue Mapping Register L18

02D0 0894 RIO_RXU_MAP_H18 Mailbox-to-Queue Mapping Register H18

02D0 0898 RIO_RXU_MAP_L19 Mailbox-to-Queue Mapping Register L19

02D0 089C RIO_RXU_MAP_H19 Mailbox-to-Queue Mapping Register H19

02D0 08A0 RIO_RXU_MAP_L20 Mailbox-to-Queue Mapping Register L20

02D0 08A4 RIO_RXU_MAP_H20 Mailbox-to-Queue Mapping Register H20

02D0 08A8 RIO_RXU_MAP_L21 Mailbox-to-Queue Mapping Register L21

02D0 08AC RIO_RXU_MAP_H21 Mailbox-to-Queue Mapping Register H21

02D0 08B0 RIO_RXU_MAP_L22 Mailbox-to-Queue Mapping Register L22

02D0 08B4 RIO_RXU_MAP_H22 Mailbox-to-Queue Mapping Register H22

02D0 08B8 RIO_RXU_MAP_L23 Mailbox-to-Queue Mapping Register L23

02D0 08BC RIO_RXU_MAP_H23 Mailbox-to-Queue Mapping Register H23

02D0 08C0 RIO_RXU_MAP_L24 Mailbox-to-Queue Mapping Register L24

02D0 08C4 RIO_RXU_MAP_H24 Mailbox-to-Queue Mapping Register H24

02D0 08C8 RIO_RXU_MAP_L25 Mailbox-to-Queue Mapping Register L25

02D0 08CC RIO_RXU_MAP_H25 Mailbox-to-Queue Mapping Register H25

02D0 08D0 RIO_RXU_MAP_L26 Mailbox-to-Queue Mapping Register L26

02D0 08D4 RIO_RXU_MAP_H26 Mailbox-to-Queue Mapping Register H26

02D0 08D8 RIO_RXU_MAP_L27 Mailbox-to-Queue Mapping Register L27

02D0 08DC RIO_RXU_MAP_H27 Mailbox-to-Queue Mapping Register H27

02D0 08E0 RIO_RXU_MAP_L28 Mailbox-to-Queue Mapping Register L28

02D0 08E4 RIO_RXU_MAP_H28 Mailbox-to-Queue Mapping Register H28

02D0 08E8 RIO_RXU_MAP_L29 Mailbox-to-Queue Mapping Register L29

02D0 08EC RIO_RXU_MAP_H29 Mailbox-to-Queue Mapping Register H29

02D0 08F0 RIO_RXU_MAP_L30 Mailbox-to-Queue Mapping Register L30

02D0 08F4 RIO_RXU_MAP_H30 Mailbox-to-Queue Mapping Register H30

02D0 08F8 RIO_RXU_MAP_L31 Mailbox-to-Queue Mapping Register L31

02D0 08FC RIO_RXU_MAP_H31 Mailbox-to-Queue Mapping Register H31

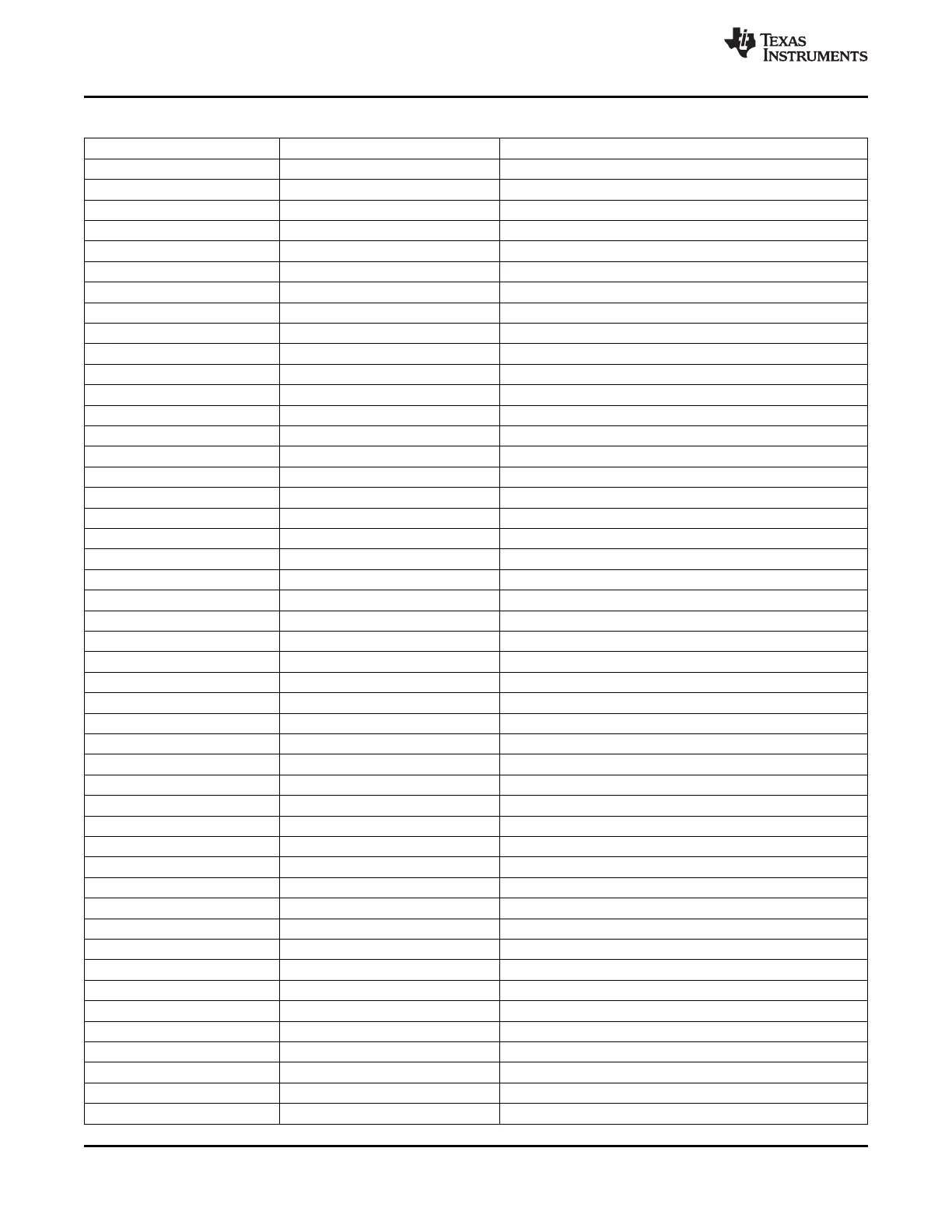

02D0 0900 RIO_FLOW_CNTL0 Flow Control Table Entry Register 0

02D0 0904 RIO_FLOW_CNTL1 Flow Control Table Entry Register 1

02D0 0908 RIO_FLOW_CNTL2 Flow Control Table Entry Register 2

02D0 090C RIO_FLOW_CNTL3 Flow Control Table Entry Register 3

02D0 0910 RIO_FLOW_CNTL4 Flow Control Table Entry Register 4

02D0 0914 RIO_FLOW_CNTL5 Flow Control Table Entry Register 5

02D0 0918 RIO_FLOW_CNTL6 Flow Control Table Entry Register 6

02D0 091C RIO_FLOW_CNTL7 Flow Control Table Entry Register 7

02D0 0920 RIO_FLOW_CNTL8 Flow Control Table Entry Register 8

02D0 0924 RIO_FLOW_CNTL9 Flow Control Table Entry Register 9

02D0 0928 RIO_FLOW_CNTL10 Flow Control Table Entry Register 10

02D0 092C RIO_FLOW_CNTL11 Flow Control Table Entry Register 11

02D0 0930 RIO_FLOW_CNTL12 Flow Control Table Entry Register 12

02D0 0934 RIO_FLOW_CNTL13 Flow Control Table Entry Register 13

02D0 0938 RIO_FLOW_CNTL14 Flow Control Table Entry Register 14

02D0 093C RIO_FLOW_CNTL15 Flow Control Table Entry Register 15

240 C64x+ Peripheral Information and Electrical Specifications Copyright © 2005–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...