TMS320C6455

www.ti.com

SPRS276M –MAY 2005–REVISED MARCH 2012

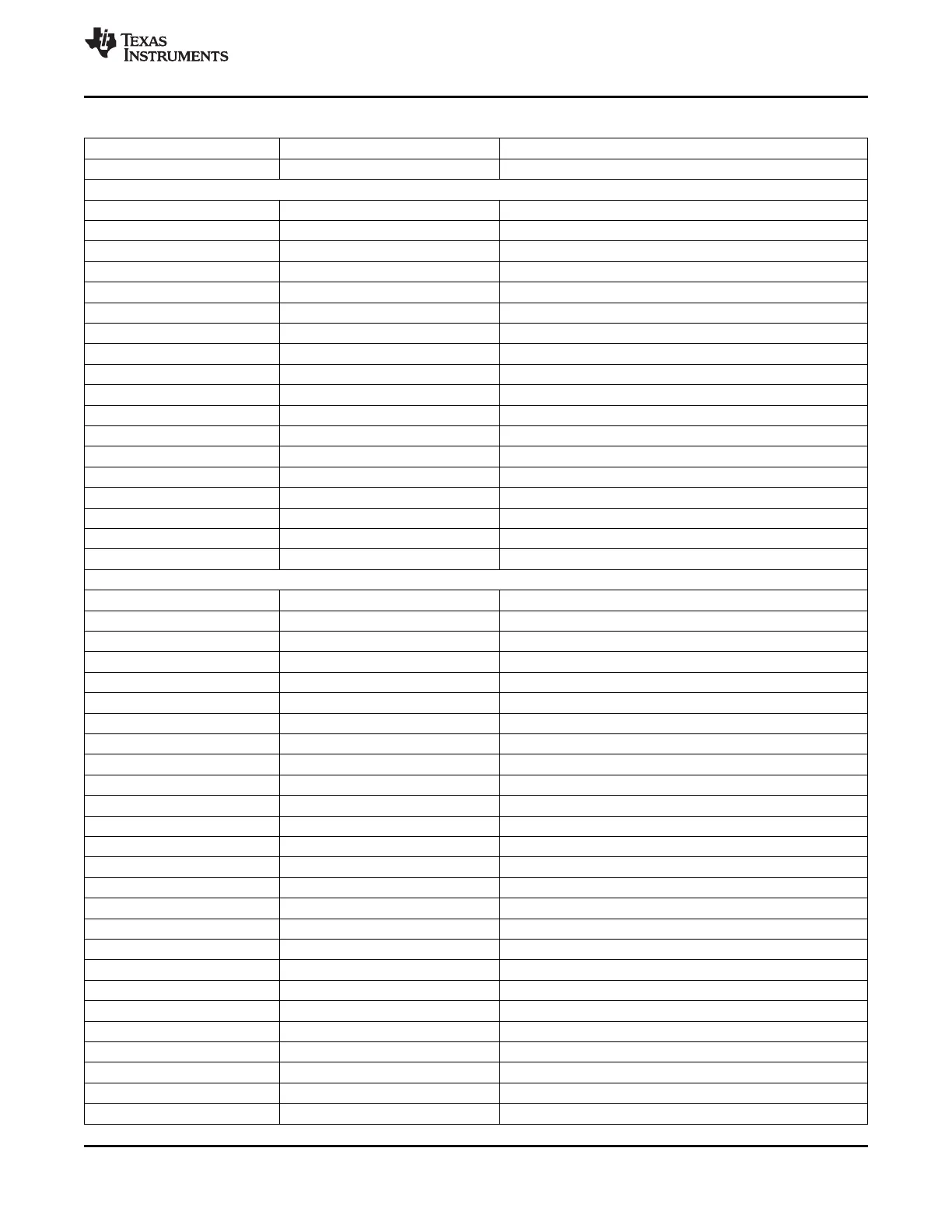

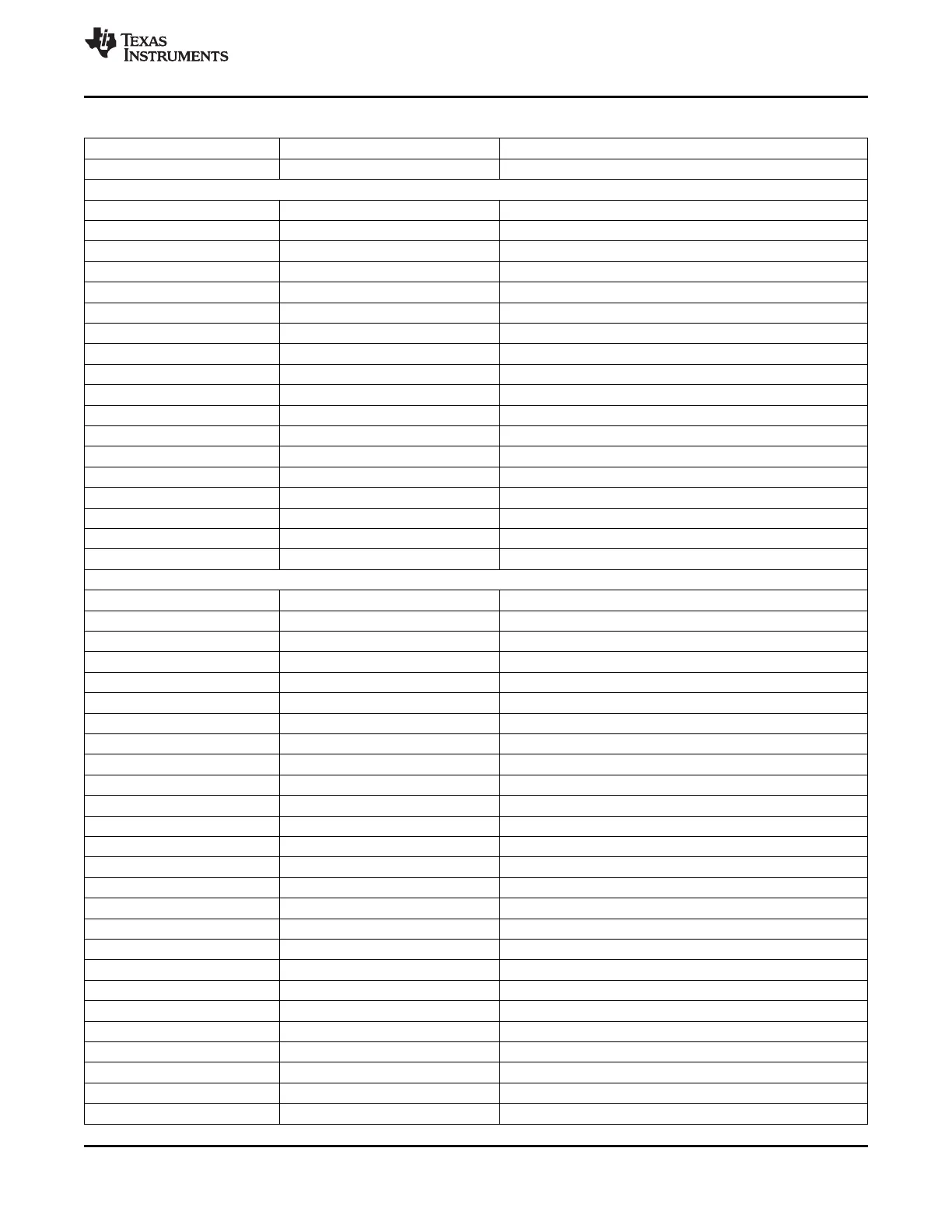

Table 7-112. RapidIO Control Registers (continued)

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02D0 0940 - 02D0 09FC - Reserved

RapidIO Peripheral-Specific Registers

02D0 1000 RIO_DEV_ID Device Identity CAR

02D0 1004 RIO_DEV_INFO Device Information CAR

02D0 1008 RIO_ASBLY_ID Assembly Identity CAR

02D0 100C RIO_ASBLY_INFO Assembly Information CAR

02D0 1010 RIO_PE_FEAT Processing Element Features CAR

02D0 1014 - Reserved

02D0 1018 RIO_SRC_OP Source Operations CAR

02D0 101C RIO_DEST_OP Destination Operations CAR

02D0 1020 - 02D0 1048 - Reserved

02D0 104C RIO_PE_LL_CTL Processing Element Logical Layer Control CSR

02D0 1050 - 02D0 1054 - Reserved

02D0 1058 RIO_LCL_CFG_HBAR Local Configuration Space Base Address 0 CSR

02D0 105C RIO_LCL_CFG_BAR Local Configuration Space Base Address 1 CSR

02D0 1060 RIO_BASE_ID Base Device ID CSR

02D0 1064 - Reserved

02D0 1068 RIO_HOST_BASE_ID_LOCK Host Base Device ID Lock CSR

02D0 106C RIO_COMP_TAG Component Tag CSR

02D0 1070 - 02D0 10FC - Reserved

RapidIO Extended Features - LP Serial Registers

02D0 1100 RIO_SP_MB_HEAD 1x/4x LP Serial Port Maintenance Block Header

02D0 1104 - 02D0 1118

02D0 1120 RIO_SP_LT_CTL Port Link Time-Out Control CSR

02D0 1124 RIO_SP_RT_CTL Port Response Time-Out Control CSR

02D0 1128 - 02D0 1138 - Reserved

02D0 113C RIO_SP_GEN_CTL Port General Control CSR

02D0 1140 RIO_SP0_LM_REQ Port 0 Link Maintenance Request CSR

02D0 1144 RIO_SP0_LM_RERIO_SP Port 0 Link Maintenance Response CSR

02D0 1148 RIO_SP0_ACKID_STAT Port 0 Local Acknowledge ID Status CSR

02D0 114C - 02D0 1154 - Reserved

02D0 1158 RIO_SP0_ERR_STAT Port 0 Error and Status CSR

02D0 115C RIO_SP0_CTL Port 0 Control CSR

02D0 1160 RIO_SP1_LM_REQ Port 1 Link Maintenance Request CSR

02D0 1164 RIO_SP1_LM_RERIO_SP Port 1 Link Maintenance Response CSR

02D0 1168 RIO_SP1_ACKID_STAT Port 1 Local Acknowledge ID Status CSR

02D0 116C - 02D0 1174 - Reserved

02D0 1178 RIO_SP1_ERR_STAT Port 1 Error and Status CSR

02D0 117C RIO_SP1_CTL Port 1 Control CSR

02D0 1180 RIO_SP2_LM_REQ Port 2 Link Maintenance Request CSR

02D0 1184 RIO_SP2_LM_RERIO_SP Port 2 Link Maintenance Response CSR

02D0 1188 RIO_SP2_ACKID_STAT Port 2 Local Acknowledge ID Status CSR

02D0 118C - 02D0 1194 - Reserved

02D0 1198 RIO_SP2_ERR_STAT Port 2 Error and Status CSR

02D0 119C RIO_SP2_CTL Port 2 Control CSR

02D0 11A0 RIO_SP3_LM_REQ Port 3 Link Maintenance Request CSR

02D0 11A4 RIO_SP3_LM_RERIO_SP Port 3 Link Maintenance Response CSR

Copyright © 2005–2012, Texas Instruments Incorporated C64x+ Peripheral Information and Electrical Specifications 241

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...