TMS320C6455

SPRS276M –MAY 2005–REVISED MARCH 2012

www.ti.com

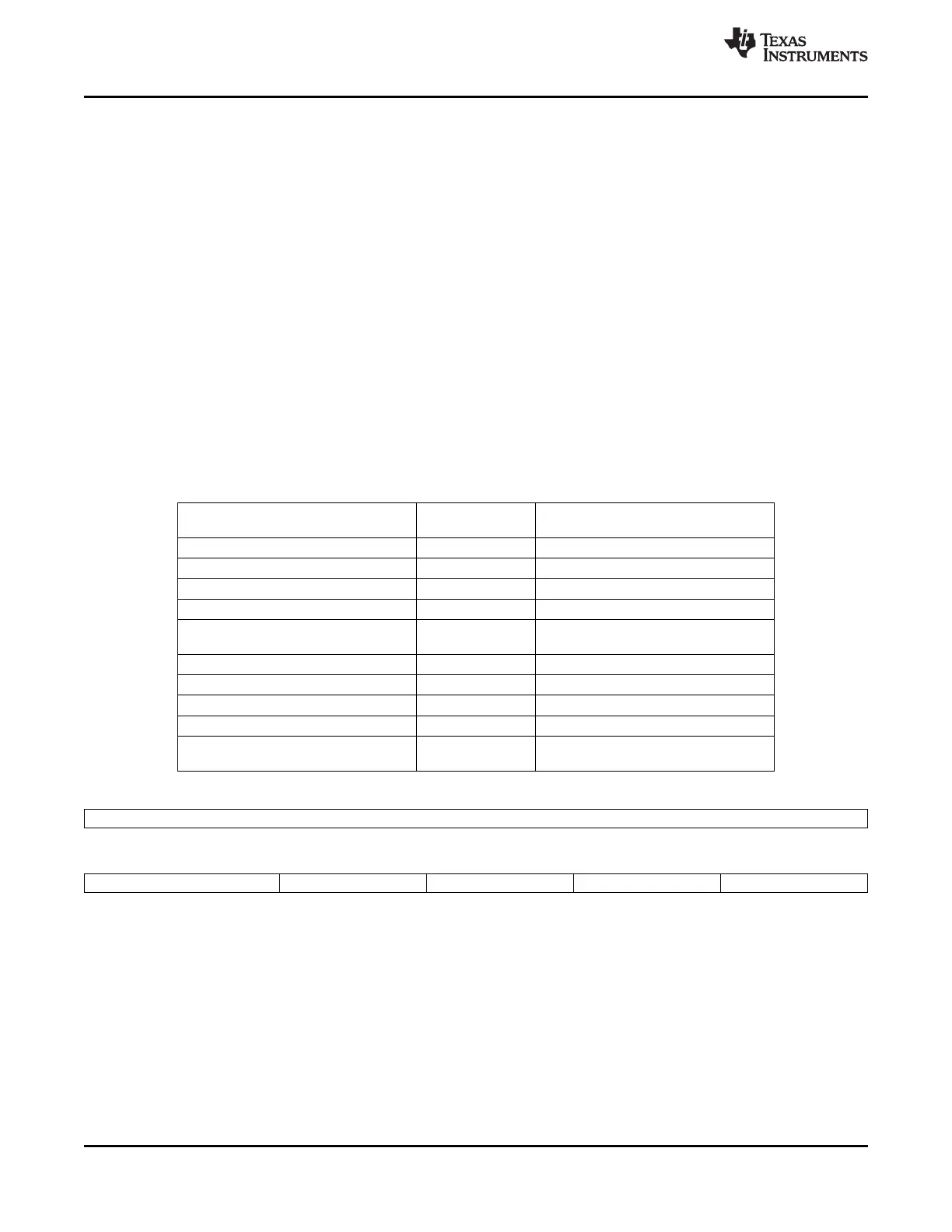

4.4 Bus Priorities

On the C6455 device, bus priority is programmable for each master. The register bit fields and default

priority levels for C6455 bus masters are shown in Table 4-2. The priority levels should be tuned to obtain

the best system performance for a particular application. Lower values indicate higher priorities. For some

masters, the priority values are programmed at the system level by configuring the PRI_ALLOC register.

Details on the PRI_ALLOC register are shown in Figure 4-3. The C64x+ megamodule , SRIO, and EDMA

masters contain registers that control their own priority values.

The priority is enforced when several masters in the system are vying for the same endpoint. Note that the

configuration SCR port on the data SCR is considered a single endpoint meaning priority will be enforced

when multiple masters try to access the configuration SCR. Priority is also enforced on the configuration

SCR side when a master (through the data SCR) tries to access the same endpoint as the C64x+

megamodule.

In the PRI_ALLOC register, the HOST field applies to the priority of the HPI and PCI peripherals. The

EMAC field specifies the priority of the EMAC peripheral. The SRIO field is used to specify the priority of

the Serial RapidIO when accessing descriptors from system memory. The priority for Serial RapidIO data

accesses is set in the peripheral itself.

Table 4-2. C6455 Default Bus Master Priorities

DEFAULT

BUS MASTER PRIORITY CONTROL

PRIORITY LEVEL

EDMA3TC0 0 QUEPRI.PRIQ0 (EDMA3 register)

EDMA3TC1 0 QUEPRI.PRIQ1 (EDMA3 register)

EDMA3TC2 0 QUEPRI.PRIQ2 (EDMA3 register)

EDMA3TC3 0 QUEPRI.PRIQ3 (EDMA3 register)

SRIO (Data Access) 0 PER_SET_CNTL.CBA_TRANS_PRI

(SRIO register)

SRIO (Descriptor Access) 0 PRI_ALLOC.SRIO

EMAC 1 PRI_ALLOC.EMAC

PCI 2 PRI_ALLOC.HOST

HPI 2 PRI_ALLOC.HOST

C64x+ Megamodule (MDMA port) 7 MDMAARBE.PRI (C64x+ Megamodule

Register)

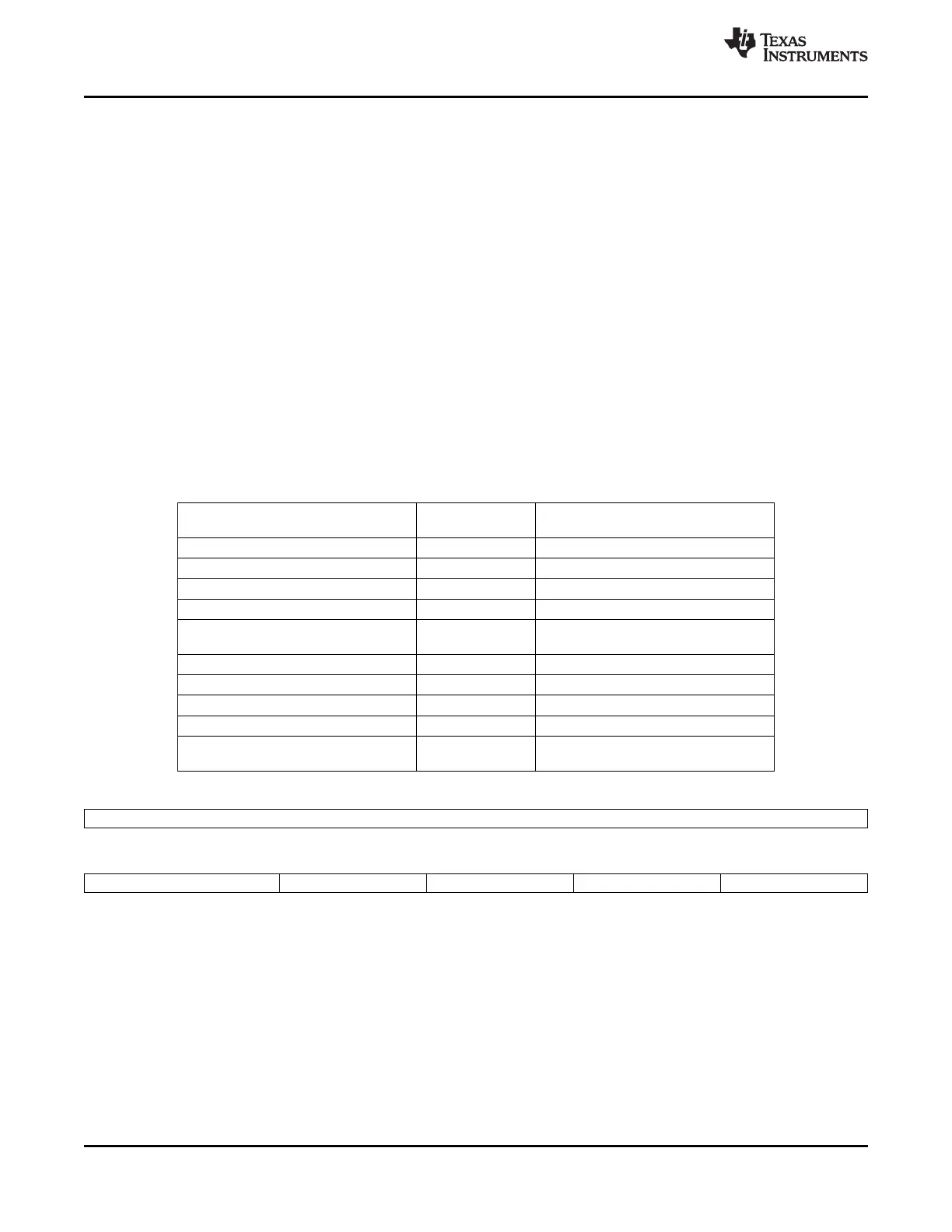

31 16

Reserved

R-0000 0000 0000 0000

15 12 11 9 8 6 5 3 2 0

Reserved SRIO Reserved HOST EMAC

R-000 0 R/W-001 R-100 R/W-010 R/W-001

LEGEND: R/W = Read/Write; R = Read only; -n = value at reset

Figure 4-3. Priority Allocation Register (PRI_ALLOC)

82 System Interconnect Copyright © 2005–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...