FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

100 Freescale Semiconductor

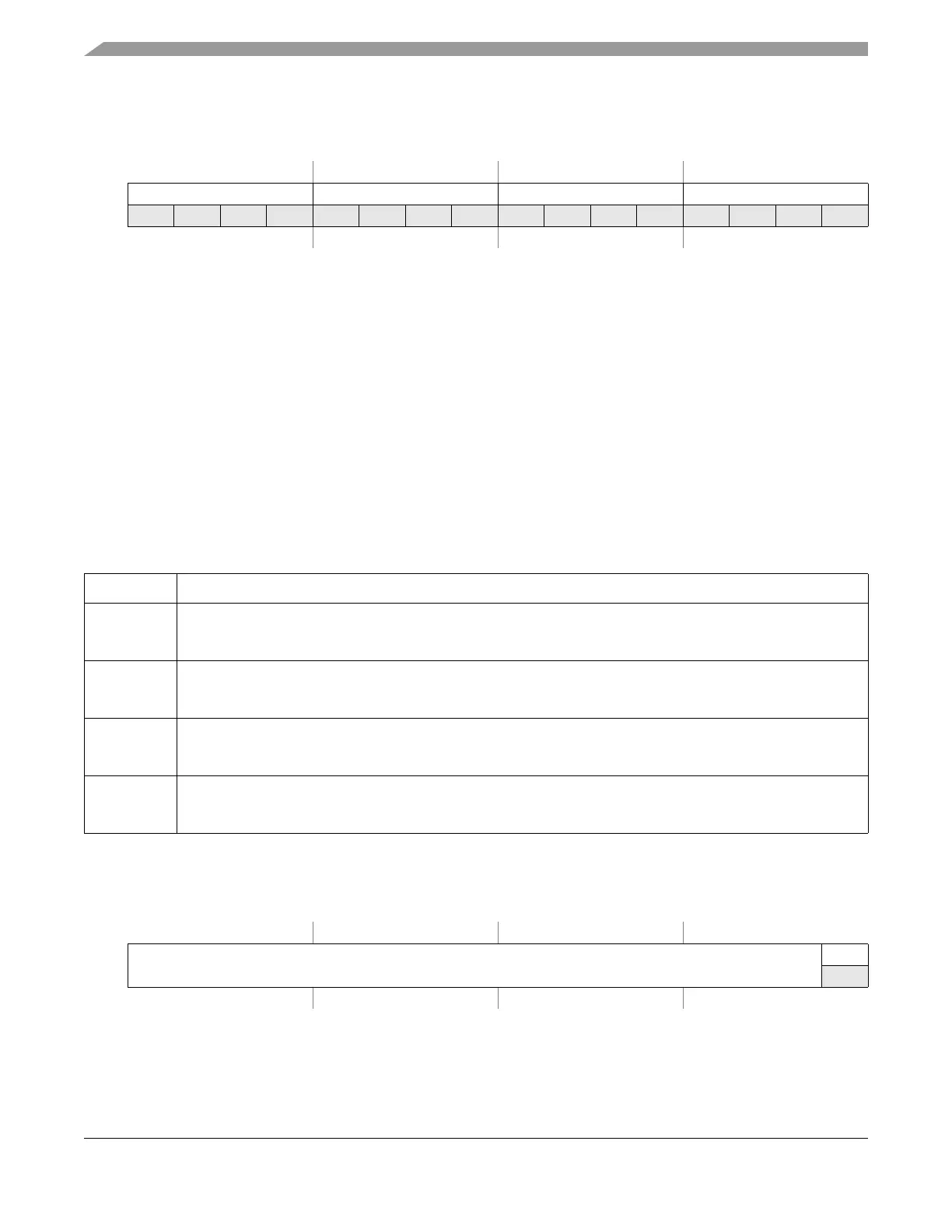

3.3.2.29 Sync Frame Counter Register (SFCNTR)

This register provides the number of synchronization frames that are used for clock synchronization in the

last even and in the last odd numbered communication cycle. This register is updated after the start of the

NIT and before 10 MT after offset correction start.

NOTE

If the application has locked the even synchronization table at the end of the

static segment of an even communication cycle, the FlexRay module does

not update the fields SFEVB and SFEVA.

If the application has locked the odd synchronization table at the end of the

static segment of an odd communication cycle, the FlexRay module does

not update the values SFODB and SFODA.

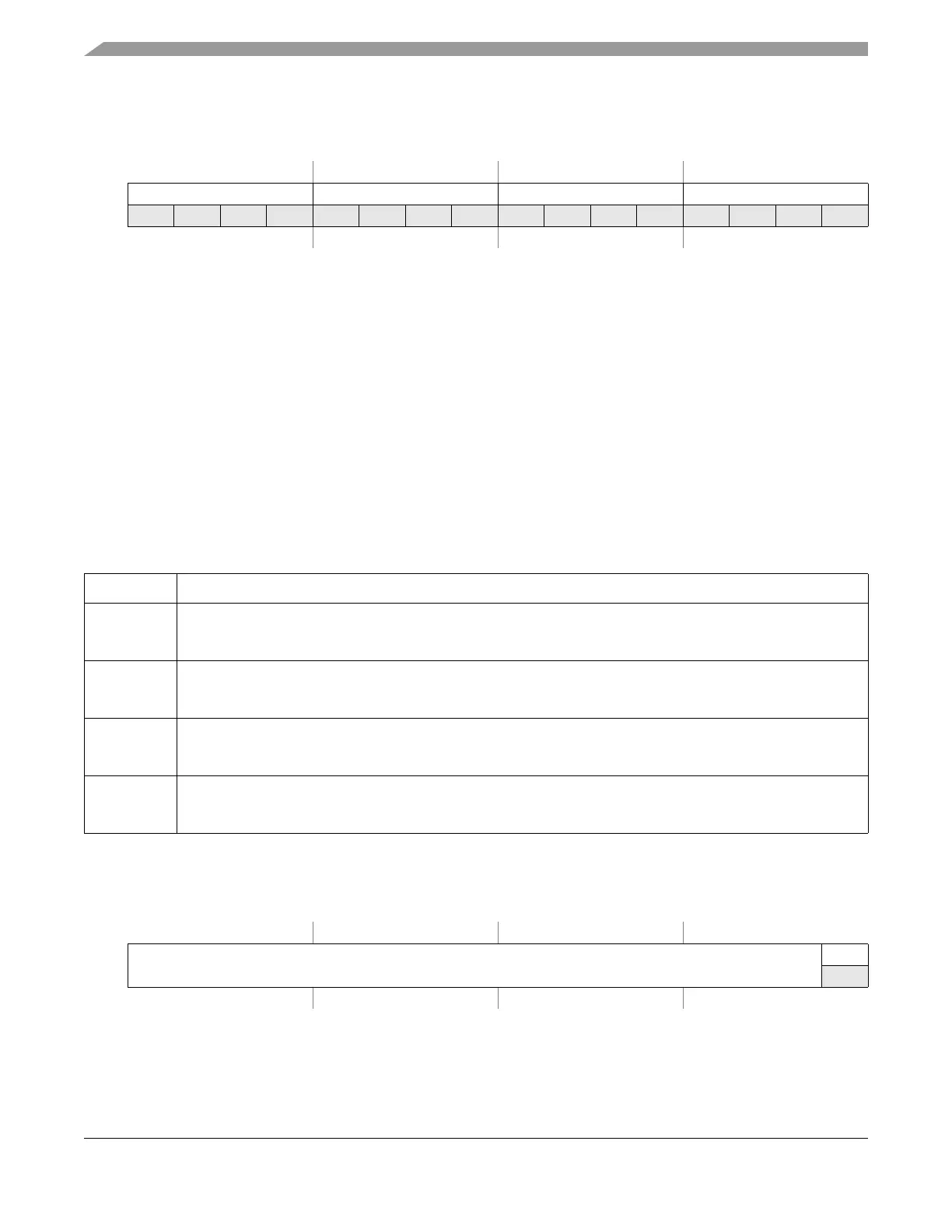

3.3.2.30 Sync Frame Table Offset Register (SFTOR)

This register defines the Flexray Memory related offset for sync frame tables. For more details, see

Section 3.4.12, “Sync Frame ID and Sync Frame Deviation Tables”.

0x0040 Additional Reset: RUN Command

1514131211109876543210

R SFEVB SFEVA SFODB SFODA

W

Reset0000000000000000

Figure 3-28. Sync Frame Counter Register (SFCNTR)

Table 3-36. SFCNTR Field Descriptions

Field Description

15–12

SFEVB

Sync Frames Channel B, even cycle — protocol related variable: size of (vsSyncIdListB for even cycle)

This field provides the size of the internal list of frame IDs of received synchronization frames used for clock

synchronization.

11–8

SFEVB

Sync Frames Channel A, even cycle — protocol related variable: size of (vsSyncIdListA for even cycle)

This field provides the size of the internal list of frame IDs of received synchronization frames used for clock

synchronization.

7–4

SFODB

Sync Frames Channel B, odd cycle — protocol related variable: size of (vsSyncIdListB for odd cycle)

This field provides the size of the internal list of frame IDs of received synchronization frames used for clock

synchronization.

3–0

SFODA

Sync Frames Channel A, odd cycle — protocol related variable: size of (vsSyncIdListA for odd cycle)

This field provides the size of the internal list of frame IDs of received synchronization frames used for clock

synchronization.

0x0042 Write: POC:config

1514131211109876543210

R

SFT_OFFSET[15:1]

0

W

Reset0000000000000000

Figure 3-29. Sync Frame Table Offset Register (SFTOR)

Loading...

Loading...