FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 75

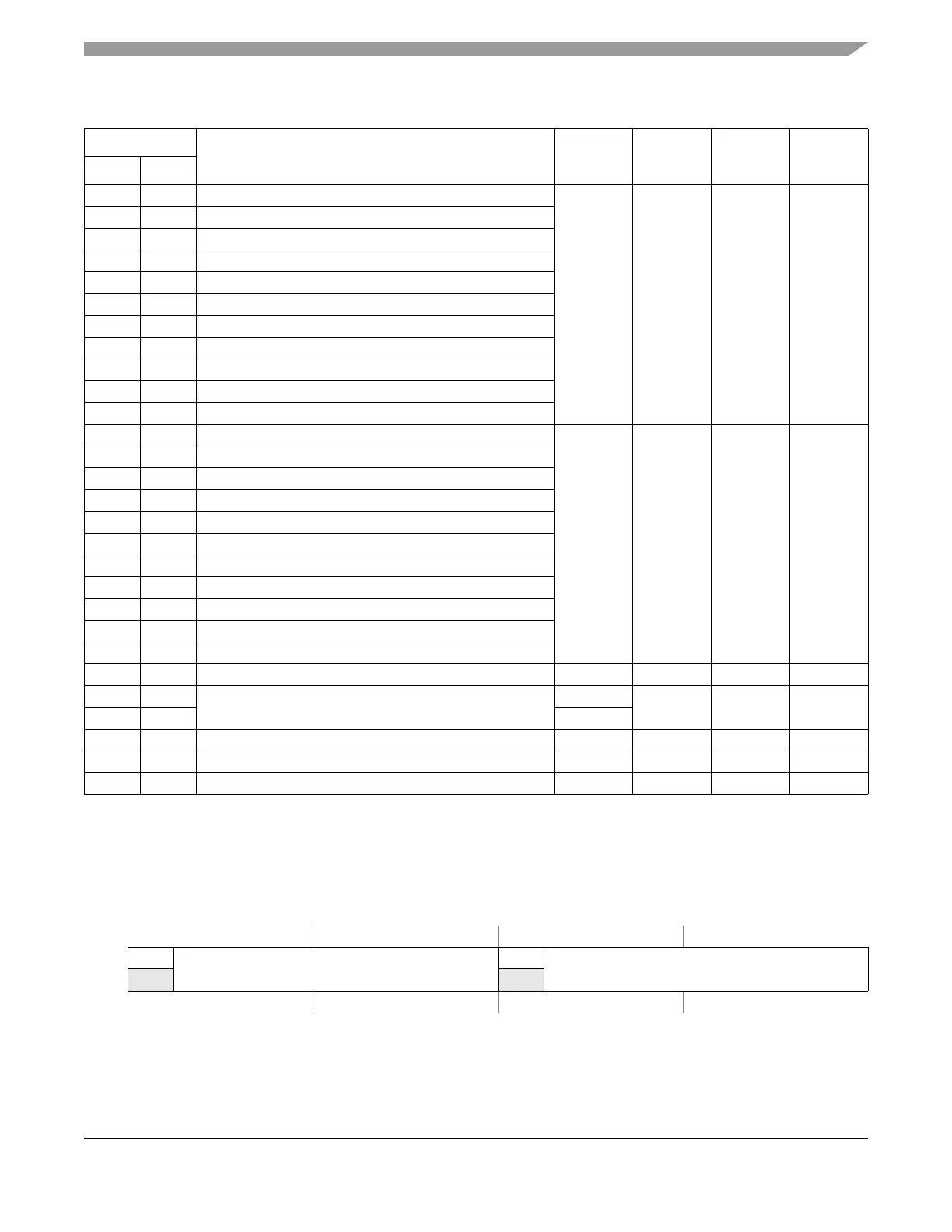

3.3.2.6 Message Buffer Data Size Register (MBDSR)

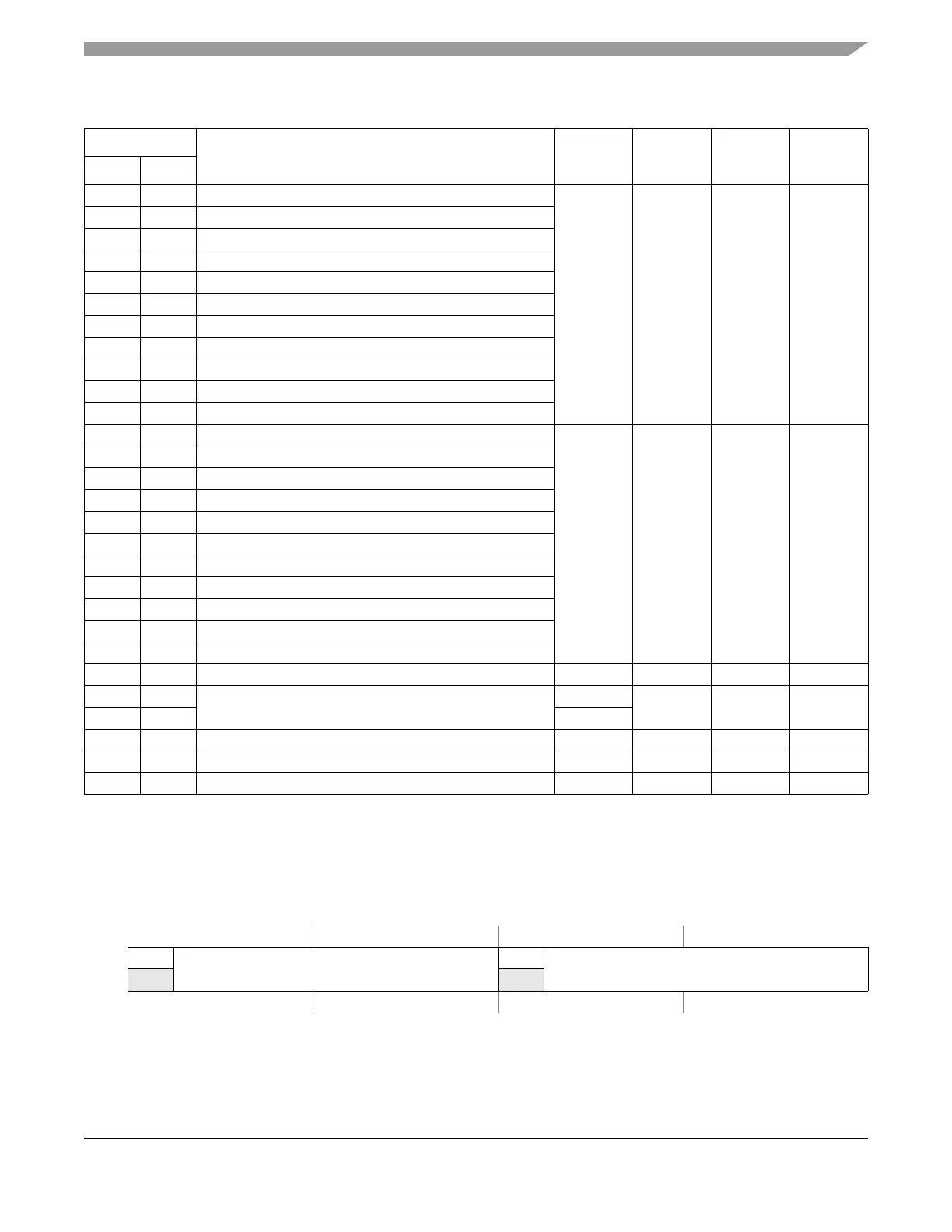

54 0x36 slot count[0]

A value 0 MT start

55 0x37 slot count[1]

56 0x38 slot count[2]

57 0x39 slot count[3]

58 0x3A slot count[4]

59 0x3B slot count[5]

60 0x3C slot count[6]

61 0x3D slot count[7]

62 0x3E slot count[8]

63 0x3F slot count[9]

64 0x40 slot count[10]

65 0x41 slot count[0]

B value 0 MT start

66 0x42 slot count[1]

67 0x43 slot count[2]

68 0x44 slot count[3]

69 0x45 slot count[4]

70 0x46 slot count[5]

71 0x47 slot count[6]

72 0x48 slot count[7]

73 0x49 slot count[8]

74 0x4A slot count[9]

75 0x4B slot count[10]

76 0x4C cycle start - pulse 0 MT start

77 0x4D

slot start

A

pulse 0 MT start

78 0x4E B

79 0x4F minislot start - pulse 0 MT start

80 0x50 arm - value +1 MT start

81 0x51 mt - value +1 MT start

1

Given in PE clock cycles

2

Indicates internal PE event not directly related to FlexRay bus timing

0x000C Write: POC:config

1514131211109876543210

R0

MBSEG2DS

0

MBSEG1DS

W

Reset0000000000000000

Figure 3-5. Message Buffer Data Size Register (MBDSR)

Table 3-12. Strobe Signal Mapping (Continued)

SEL

Description Channel Type Offset

1

Reference

dec hex

Loading...

Loading...