Port Integration Module (PIM)

MFR4310 Reference Manual, Rev. 2

210 Freescale Semiconductor

4.3.1 Port Integration Module Registers

4.3.1.1 Part ID Register (PIDR)

This register provides the part ID (4310) in binary coded decimal.

4.3.1.2 ASIC Version Number Register (AVNR)

This register provides the ASIC version number in binary coded decimal. The content of this register is

dependent on the maskset number. Figure 4-2 shows the content and reset values for maskset 1M63J. See

Section 2.3.2, “Part ID and Module Version Number Assignments” for details of maskset numbers.

4.3.1.3 Host Interface Pins Drive Strength Register (HIPDSR)

This register controls the drive strength of the host interface, interrupt, debug, and output clock pins.

0x00FA Host Interface Pins Pullup/pulldown Control Register (HIPPCR) R/W

0x00FC Physical Layer Pins Pullup/pulldown Enable Register (PLPPER) R/W

0x00FE Physical Layer Pins Pullup/pulldown Control Register (PLPPCR) R/W

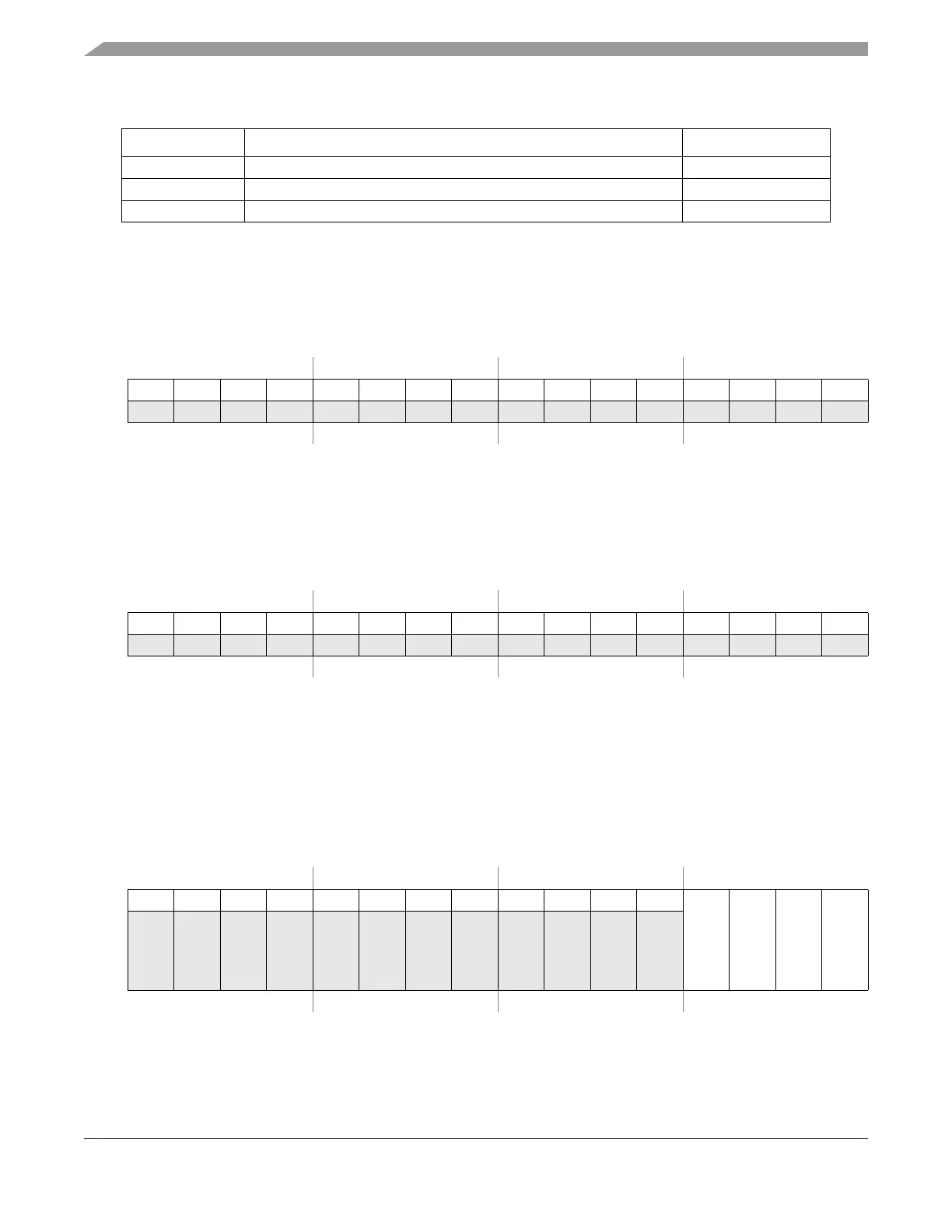

Address in MFR4310 = 0x00F0

1514131211109876543210

R0100001100000000

W

Reset0100001100010000

Figure 4-1. Part ID Register (PIDR)

Address in MFR4310 = 0x00F2

1514131211109876543210

R0000000000000001

W

Reset0000000000000001

Figure 4-2. ASIC Version Number Register (AVNR) (for Maskset 1M63J)

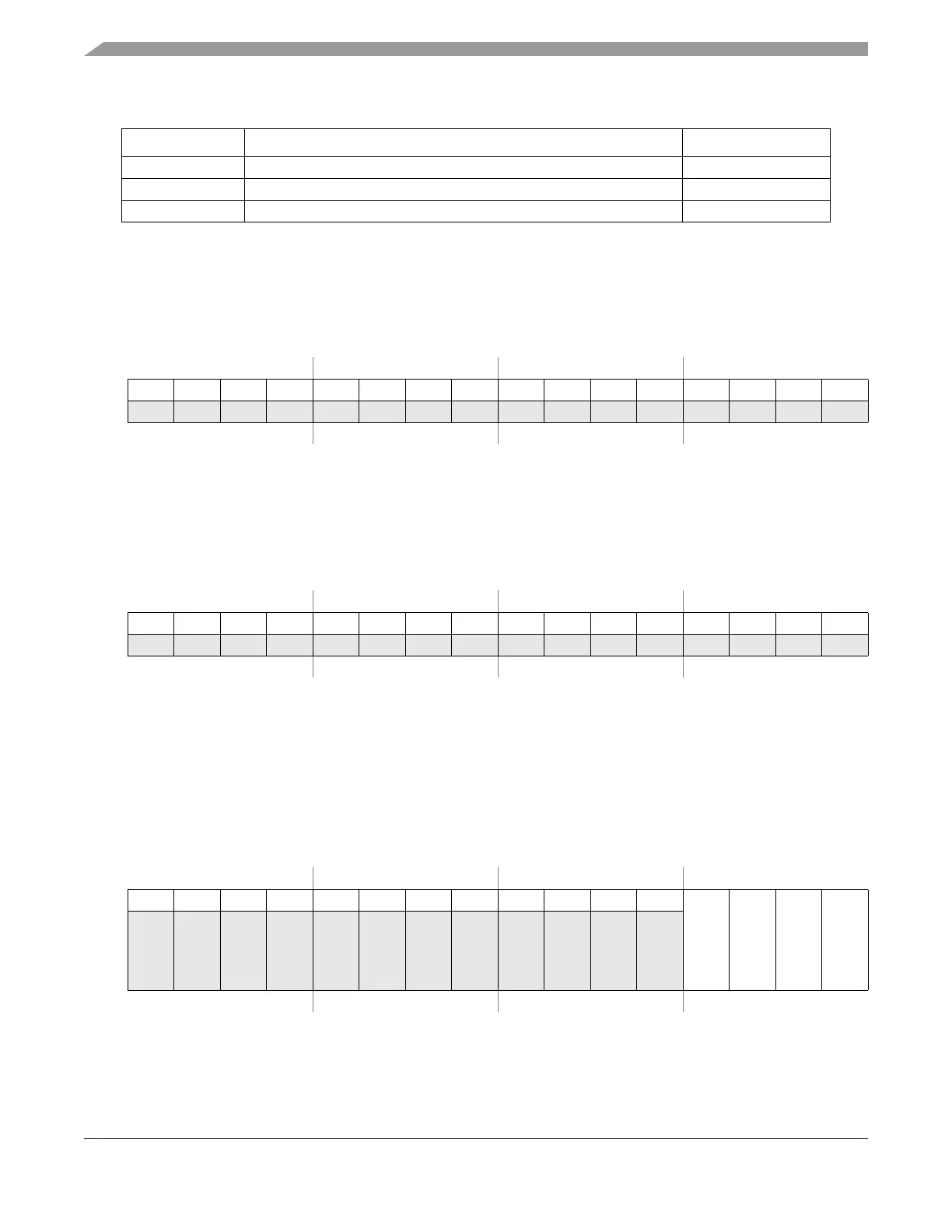

Address in MFR4310 = 0x00F4 Write: Any Time

1514131211109876543210

R000000000000

CLKOUT

DBG[3:2]

INT_CC#

D[0:15]/

PA[0:7]/PB[0:7]

W

Reset0000000000001111

Figure 4-3. Host Interface Pins Drive Strength Register (HIPDSR)

Table 4-3. Port Integration Module Memory Map

Address Use Access

Loading...

Loading...