PIM Memory Map and Registers

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 211

4.3.1.4 Physical Layer Pins Drive Strength Register (PLPDSR)

This register controls the drive strength of the FlexRay physical layer pins.

Table 4-4. HIPDSR Field Descriptions

Field Description

0

D[0:15]/

PA[0:7]/PB[0:7]

Host interface output data drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

1

INT_CC#

Interrupt output drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

2

DBG[3:2]

Debug output (bits 3 and 2 only) drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

3

CLKOUT

Output clock drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

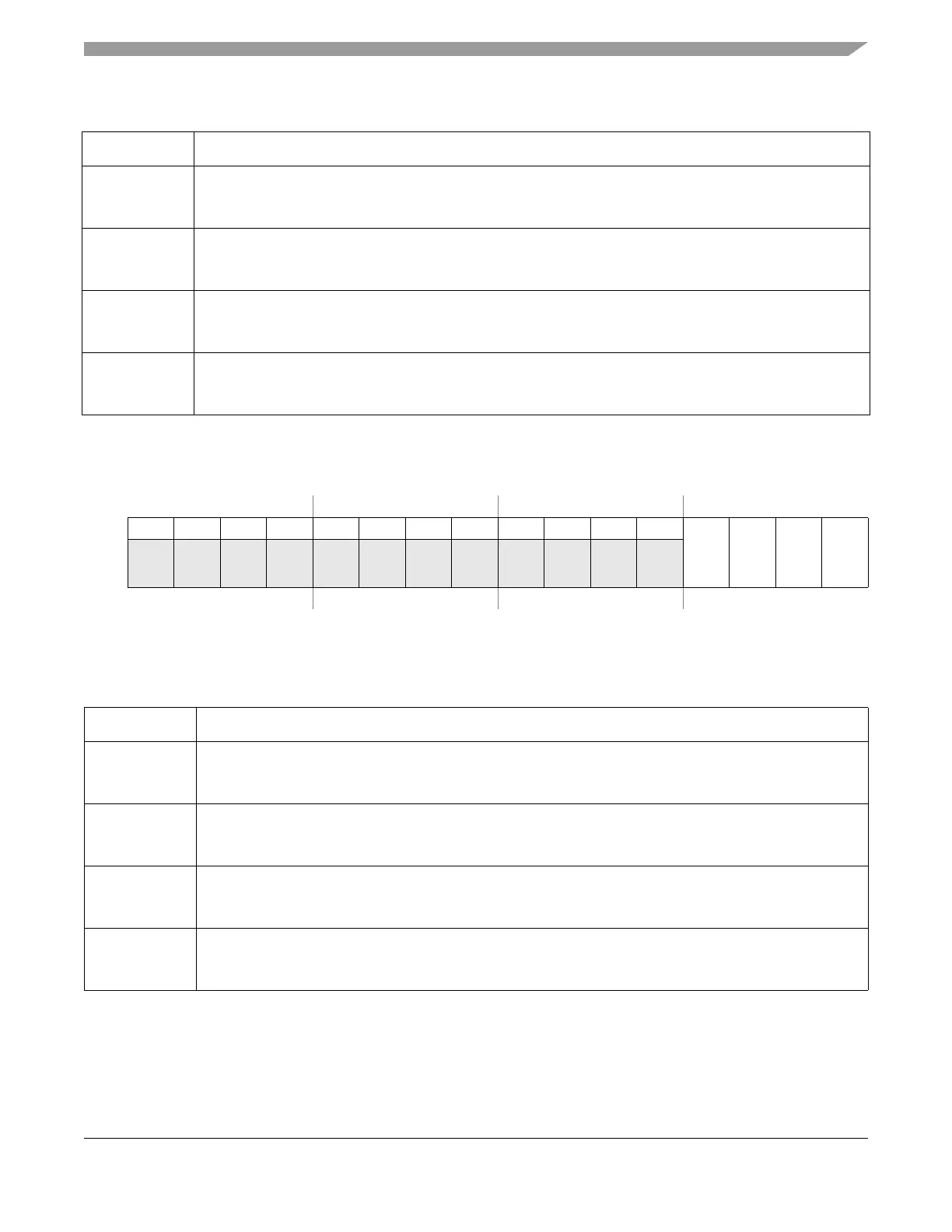

Address in MFR4310 = 0x00F6 Write: Any Time

1514131211109876543210

R000000000000

TXD_BG2

TXD_BG1

TXEN2#

TXEN1#

W

Reset0000000000001111

Figure 4-4. Physical Layer Pins Drive Strength Register (PLPDSR)

Table 4-5. PLPDSR Field Descriptions

Field Description

0

TXEN1#

Transmit enable (channel A) output drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

1

TXEN2#

Transmit enable (channel B) output drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

2

TXD_BG1

Transmit data (channel A) output drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

3

TXD_BG2

Transmit data (channel B) output drive strength control

0 Pin drive strength is reduced to 1/3 of full strength

1 Pin drive strength is full

Loading...

Loading...