FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 99

This register provides five combined interrupt flags and a copy of three individual interrupt flags. The

combined interrupt flags are the result of a binary OR of the values of other interrupt flags regardless of

the state of the interrupt enable bits. The generation scheme for the combined interrupt flags is depicted in

Figure 3-142. The individual interrupt flags WUPIF, FNEBIF, and FNEAIF are copies of corresponding

flags in the Global Interrupt Flag and Enable Register (GIFER) and are provided here to simplify the

application interrupt flag check. To clear the individual interrupt flags, the application must use the Global

Interrupt Flag and Enable Register (GIFER).

NOTE

The meanings of the five combined status bits MIF, PRIF, CHIF, RBIF, and

TBIF are different from those mentioned in the Global Interrupt Flag and

Enable Register (GIFER).

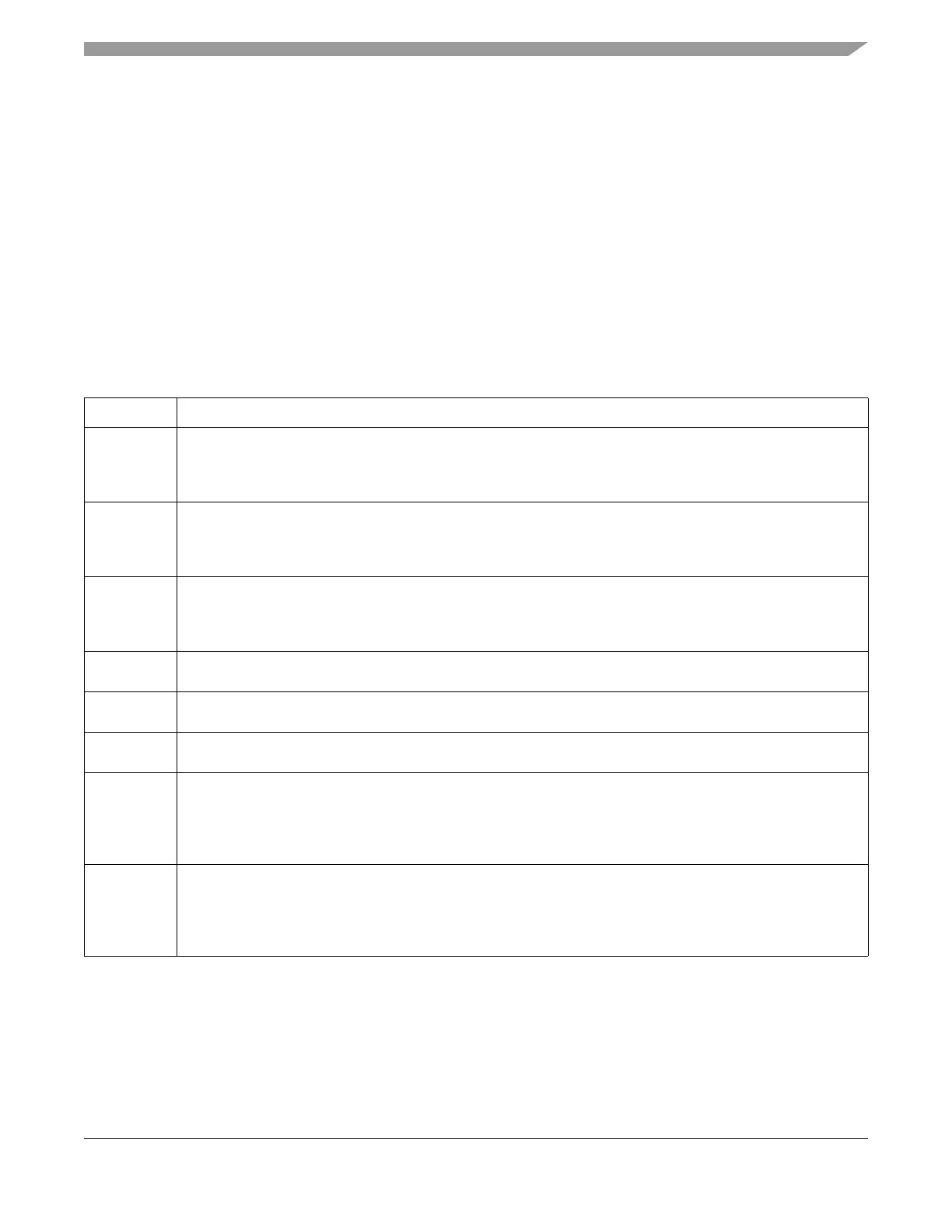

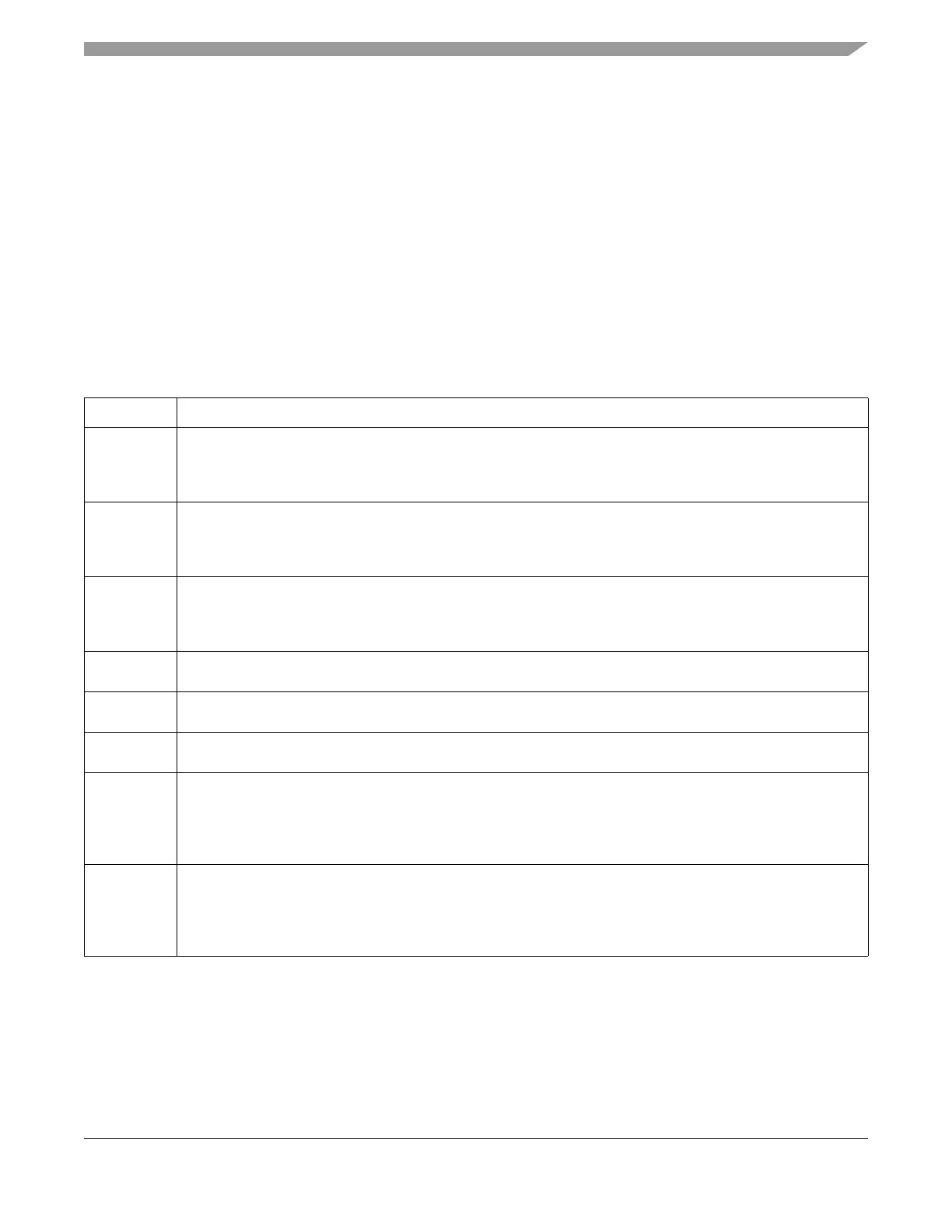

Table 3-35. CIFRR Field Descriptions

Field Description

7

MIF

Module Interrupt Flag — This flag is set if there is at least one interrupt source that has its interrupt flag

asserted.

0 No interrupt source has its interrupt flag asserted

1 At least one interrupt source has its interrupt flag asserted

6

PRIF

Protocol Interrupt Flag — This flag is set if at least one of the individual protocol interrupt flags in the Protocol

Interrupt Flag Register 0 (PIFR0) or Protocol Interrupt Flag Register 1 (PIFR1) is equal to 1.

0 All individual protocol interrupt flags are equal to 0

1 At least one of the individual protocol interrupt flags is equal to 1

5

CHIF

CHI Interrupt Flag — This flag is set if at least one of the individual CHI error flags in the CHI Error Flag Register

(CHIERFR) is equal to 1.

0 All CHI error flags are equal to 0

1 At least one CHI error flag is equal to 1

4

WUPIF

Wakeup Interrupt Flag — Provides the same value as GIFER{WUPIF]

3

FNEBIF

Receive FIFO channel B Not Empty Interrupt Flag — Provides the same value as GIFER[FNEBIF]

2

FNEAIF

Receive FIFO channel A Not Empty Interrupt Flag — Provides the same value as GIFER[FNEAIF]

1

RBIF

Receive Message Buffer Interrupt Flag — This flag is set if for at least one of the individual receive message

buffers (MBCCSRn[MTD] = 0) the interrupt flag MBIF in the corresponding Message Buffer Configuration,

Control, Status Registers (MBCCSRn) is equal to 1.

0 None of the individual receive message buffers has the MBIF flag asserted.

1 At least one individual receive message buffers has the MBIF flag asserted.

0

TBIF

Transmit Message Buffer Interrupt Flag — This flag is set if for at least one of the individual single or double

transmit message buffers (MBCCSRn[MTD] = 1) the interrupt flag MBIF in the corresponding Message Buffer

Configuration, Control, Status Registers (MBCCSRn) is equal to 1.

0 None of the individual transmit message buffers has the MBIF flag asserted.

1 At least one individual transmit message buffers has the MBIF flag asserted.

Loading...

Loading...