FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

202 Freescale Semiconductor

3.4.20 Clock Domain Crossing

The Clock Domain Crossing module CDC implements the signal crossing from the CHI clock domain to

the PE clock domain and vice versa. The signal crossing logic is implemented as a three-stage pipe-line.

Two pipe-line stages are used for clock synchronization; the third stage is used for pulse generation.

3.4.20.1 Clock Domain Crossing Signal Latency

Due to the clock domain crossing implementation, each signal from the PE to the CHI is delayed by at least

two CHI clock cycles and by at most three CHI clock cycles. In terms of time, the signal latency time t

lat

for a given CHI frequency f

chi

is

Eqn. 3-26

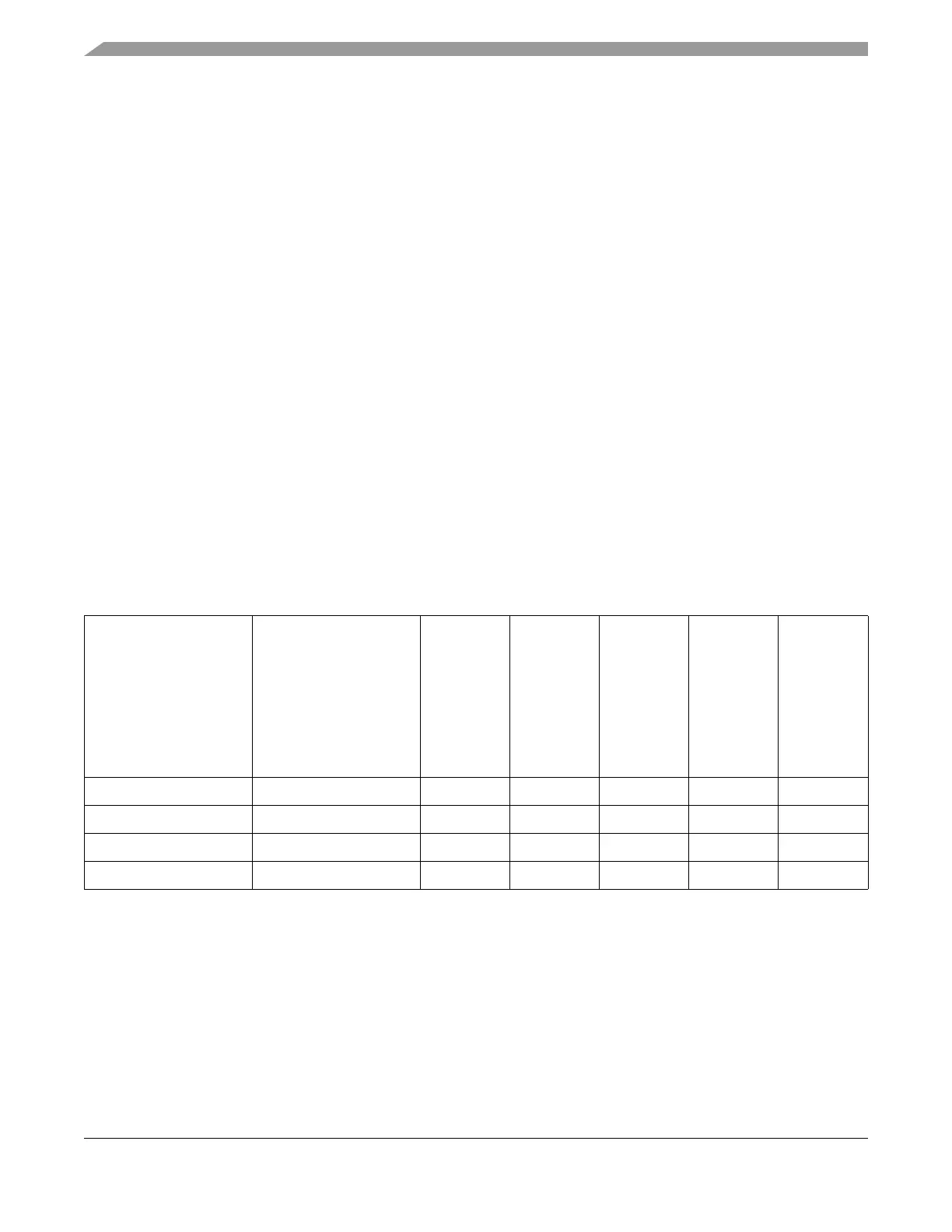

3.5 Lower FlexRay Bit Rate Support

The FlexRay module supports a number of lower bit rates on the FlexRay bus channels. The lower bit rates

are implemented by modifying the duration of the microtick pdMicrotick, the number of samples per

microtick pSamplesPerMicrotick, the number of samples per bit cSamplesPerBit, and the strobe offset

cStrobeOffset. The application configures the FlexRay channel bit rate by setting the BITRATE field in the

Module Configuration Register (MCR). The protocol values are set internally. The available bit rates, the

related BITRATE field configuration settings and related protocol parameter values are shown in

Table 3-110.

NOTE

The bit rate of 8 Mbit/s is not defined by the FlexRay Communications

System Protocol Specification, Version 2.1 Rev A.

3.6 Initialization Information

This section provides information for initializing and using the FlexRay module.

Table 3-110. FlexRay Channel Bit Rate Control

FlexRay Channel

Bit Rate

[Mbit/s]

MCR.BITRATE

pdMicrotick

[ns]

gdSampleClockPeriod

[ns]

pSamplesPerMicrotick

cSamplesPerBit

cStrobeOffset

10.0 000 25.0 12.5 2 8 5

8.0 011 25.0 12.5 2 10 6

5.0 001 25.0 25.0 1 8 5

2.5 010 50.0 50.0 1 8 5

2

f

chi

--------

t

lat

3

f

chi

--------

≤≤

Loading...

Loading...