FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

186 Freescale Semiconductor

3.4.11 External Clock Synchronization

The application of the external rate and offset correction is triggered when the application writes to the

EOC_AP and ERC_AP fields in the Protocol Operation Control Register (POCR). The PE applies the

external correction values in the next even-odd cycle pair as shown in Figure 3-132 and Figure 3-133.

NOTE

The values provided in the EOC_AP and ERC_AP fields are the values that

were written from the application most recently. If these value were already

applied, they are not applied in the current cycle pair again.

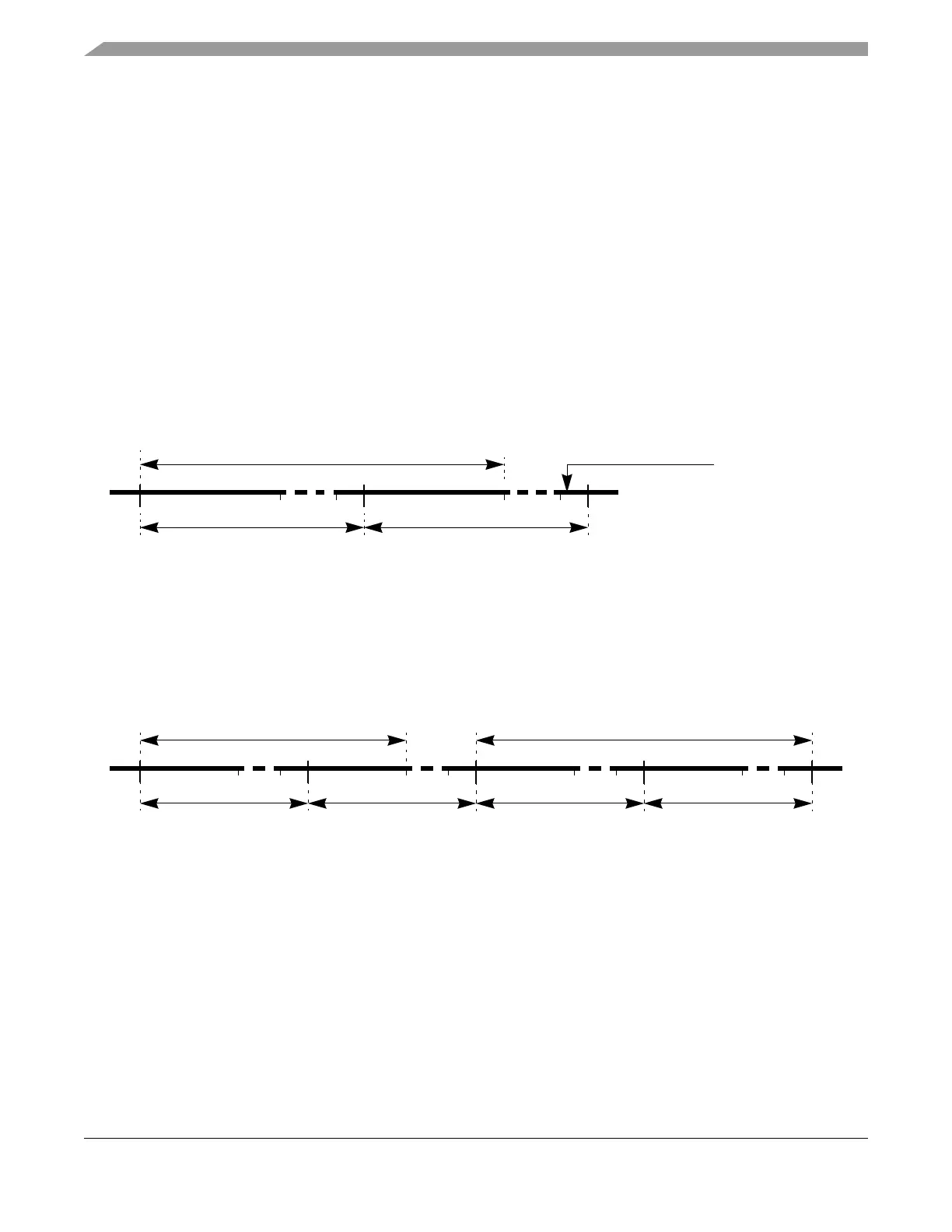

If the offset correction applied in the NIT of cycle 2n+1 shall be affect by the external offset correction,

the EOC_AP field must be written to after the start of cycle 2n and before the end of the static segment of

cycle 2n+1. If this field is written to after the end of the static segment of cycle 2n+1, it is not guaranteed

that the external correction value is applied in cycle 2n+1. If the value is not applied in cycle 2n+1, the

value is applied in the cycle 2n+3. Refer to Figure 3-132 for timing details.

Figure 3-132. External Offset Correction Write and Application Timing

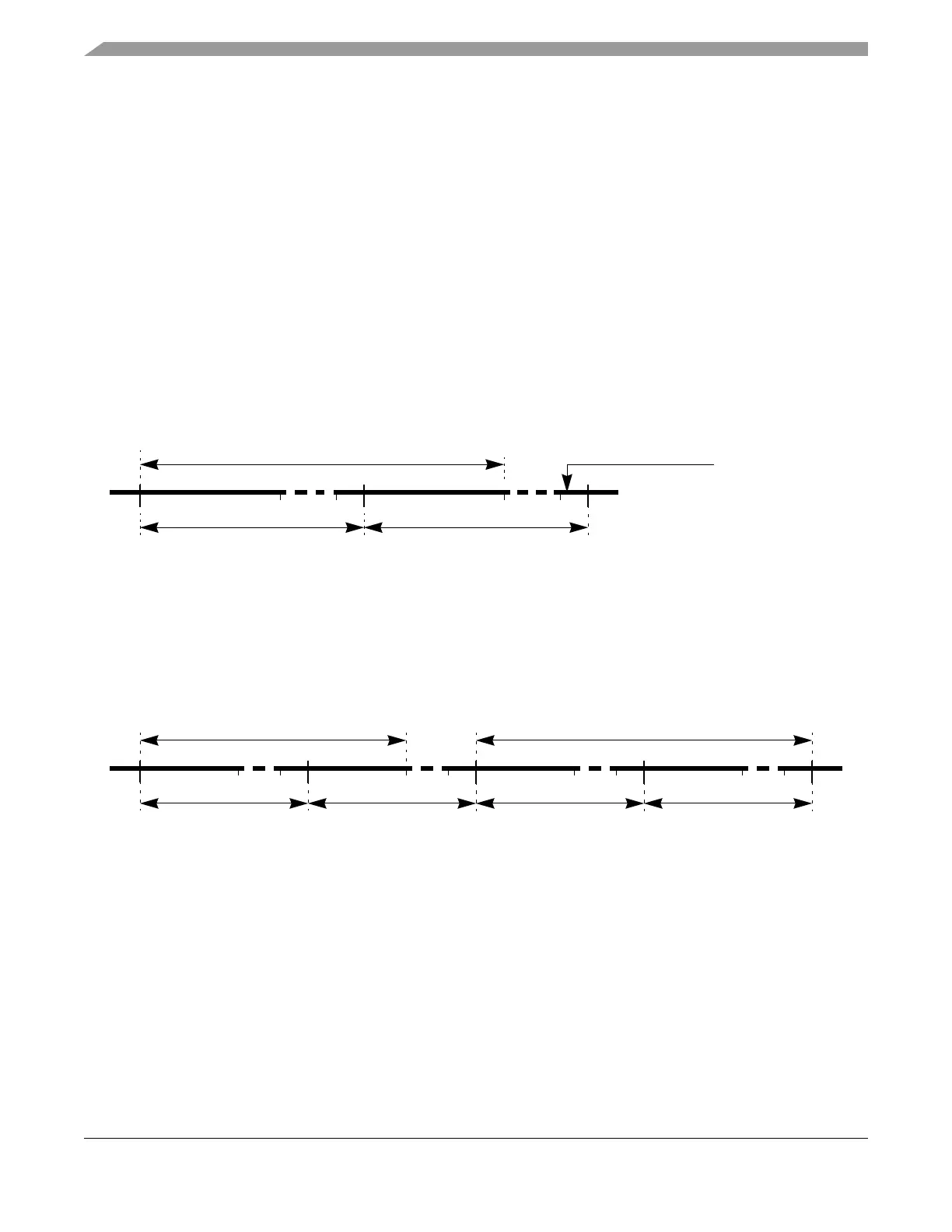

If the rate correction for the cycle pair [2n+2, 2n+3] shall be affect by the external offset correction, the

ERC_AP field must be written to after the start of cycle 2n and before the end of the static segment start

of cycle 2n+1. If this field is written to after the end of the static segment of cycle 2n+1, it is not guaranteed

that the external correction value is applied in cycle pair [2n+2, 2n+3]. If the value is not applied for cycle

pair [2n+2, 2n+3], the value is be applied for cycle pair [2n+4, 2n+5]. Refer to Figure 3-133 for details.

Figure 3-133. External Rate Correction Write and Application Timing

3.4.12 Sync Frame ID and Sync Frame Deviation Tables

The FlexRay protocol requires the provision of a snapshot of the Synchronization Frame ID tables for the

even and odd communication cycle for both channels. The FlexRay module provides the means to write a

copy of these internal tables into the FRM and ensures application access to consistent tables by means of

table locking. After the application has locked the table successfully, the FlexRay module does not

overwrite these tables and the application can read a consistent snapshot.

static segment NIT static segment NIT

EOC_AP write window EOC_AP application

cycle 2n cycle 2n+1

static segment NIT

ERC_AP write window ERC_AP application

cycle 2n

static segment NIT

cycle 2n+1

static segment NIT

cycle 2n+2

static segment NIT

cycle 2n+3

Loading...

Loading...